Tel.: +34 91 706 56 69

Poema Sinfónico, 27. Esc B. Planta 1 Pta 5

28054 (Madrid - SPAIN)

e-mail: gm2@gm2publicacionestecnicas.com ó consultas@convertronic.net

Ordenadores sobre ruedas. Así es como la gente ve actualmente a los automóviles. Prácticamente todo lo que sucede en un vehículo está siendo monitorizado y actuado por un microcontrolador, desde abrir ventanas hasta calcular la mezcla óptima de combustible-aire para la demanda de torque actual. Pero apenas hemos arañado la superficie en términos de cuánta potencia de cálculo se está incorporando a los vehículos.

Auge en vehículos autónomos de Nivel 3 y robotaxis

La era del transporte autónomo está amaneciendo y con ella traerá una nueva era de requisitos de cálculo para la industria automotriz. Los vehículos automatizados requieren extensos conjuntos de sensores para escanear el entorno y proporcionar al automóvil los datos que necesita para emular la conducción humana. El informe "Autonomous Cars and Robotaxis 2024-2044" de IDTechEx encontró que los principales robotaxis de nivel 4 de la SAE tienen hasta 40 sensores individuales. Combinado con el próximo despliegue de tecnologías automatizadas en el mercado de vehículos, esto impulsará una TACC de 13% en el mercado de sensores automotrices durante 10 años. Sin embargo, los sensores por sí solos son casi inútiles sin una computación de alto rendimiento que procese sus datos y construya una representación tridimensional del entorno para informar la política de conducción programada del vehículo.

Cálculo de Alto Rendimiento (HPC) para vehículos autónomos

Fuente: IDTechEx

Ya sea que se utilice la fusión tardía o temprana, la HPC aún tendrá mucho procesamiento de datos que realizar en forma de procesamiento de imágenes y ejecución de algoritmos de inteligencia artificial para la clasificación de imágenes y la política de conducción. Los componentes clave que manejan estas tareas son los procesadores gráficos (GPUs), procesadores de cálculo (CPUs) y la memoria RAM. Típicamente, estos son componentes discretos separados; sin embargo, los requisitos específicos de la HPC para vehículos autónomos han llevado a combinarlos en chips individuales llamados SOC o sistemas en chips. Estos combinan GPUs, CPUs, RAM y más en una sola pieza de silicio. El SOC ideal puede recibir datos de todos los sensores de conducción autónoma del vehículo, procesarlos, identificar y clasificar todos los objetos detectados y crear un conjunto de actuaciones de dirección, aceleración y freno según la política de conducción.

Colocar todas estas funciones en un solo chip es clave para cumplir con los requisitos computacionales de la conducción autónoma. Con casi ninguna separación física, cada parte del chip puede intercambiar datos con una latencia cercana a cero, casi sin ruido y con un ancho de banda enorme. Esto se opone a tener componentes discretos distribuidos en una PCB, con más interfaces y más trazas de datos que introducen ruido y latencia.

Un Futuro de Tecnologías Semiconductoras en Crecimiento

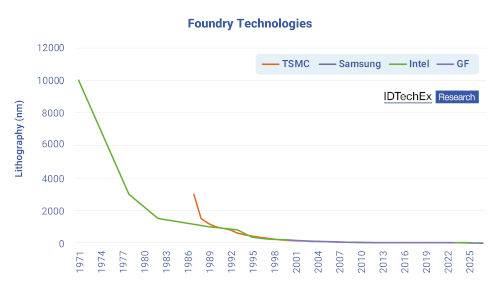

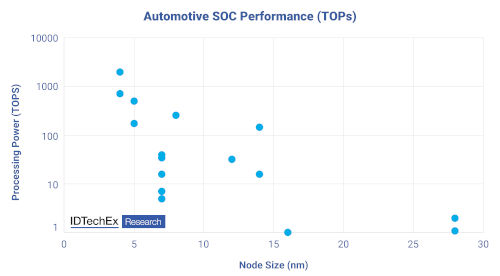

En los últimos años, IDTechEx ha observado que empresas como Mobileye, Nvidia y otras han avanzado desde los 28nm en 2018 hasta soluciones de 7nm FinFET y menos en 2021. Sin embargo, las fundiciones ahora están produciendo tecnologías sub-5nm y avanzando hacia tecnologías sub-1nm en el futuro. Cada vez que la tecnología de nodo se reduce a la mitad, la potencia de cálculo aumenta en un factor de 10. Pero perseguir tamaños de nodo cada vez más pequeños se volverá más costoso. Una sola oblea de 300 mm de la tecnología de 3nm de TSMC cuesta alrededor de US$20,000, y ese precio continuará aumentando a medida que se exijan tecnologías sub-3nm en diversas industrias, desde aplicaciones de cómputo normales como teléfonos, computadoras portátiles y PC, hasta la nueva demanda proveniente del sector automotriz.

Desafíos y Oportunidades para la HPC Automotriz

Fuente: IDTechEx

Dado este escenario, los desarrolladores de HPC automotrices necesitan pensar en cómo optimizar las tecnologías existentes para obtener el máximo rendimiento. Un enfoque que IDTechEx está observando es un mayor enfoque en aceleradores de inteligencia artificial (IA), redes neuronales (NN) y aprendizaje profundo (DL). Estos utilizan nuevas estrategias de procesamiento de datos mejoradas por IA, reduciendo la dependencia de los enfoques clásicos encontrados en la GPU. Esto puede aumentar el rendimiento del chip de manera muy económica, requiriendo menos inversión en tecnologías de nodo más pequeñas y produciendo incluso un beneficio general de eficiencia. IDTechEx está viendo que la IA se vuelve más común en los diagramas de bloques SOC de los principales proveedores de nivel 2, como Mobileye y Renesas. Pero una perspectiva particularmente interesante es Recogni. Recogni es una startup que ha desarrollado un acelerador de IA para aplicaciones SOC de conducción autónoma que promete un cambio de juego en potencia computacional y eficiencias.

Incluso con la reducción de los tamaños de nodo y soluciones de IA imaginativas, la industria de chips de computadora más grande aún está viendo una desaceleración en el ritmo de desarrollo. La ley de Moore establece que la potencia computacional debería duplicarse cada dos años, una fórmula empírica de décadas que se ha mantenido fuerte hasta hace poco. Algunos dicen que la ley de Moore está comenzando a desacelerar a medida que la industria enfrenta desafíos tecnológicos cada vez más difíciles para lograr ganancias incrementales más pequeñas. Otros dicen que la ley de Moore está muerta.

Avances en encapsulado de Semiconductores: Chiplets y Más

Fuente: IDTechEx

Una Solución Destacada para Afrontar la Desaceleración de la Ley de Moore y el Substancial Aumento en el Costo de Fabricación de Circuitos Integrados Monolíticos (CIs) es el Concepto de "Chiplets".

El concepto central de los chiplets implica descomponer un CI monolítico en bloques funcionales distintos, transformar estos bloques en chiplets separados y luego volver a ensamblarlos a nivel de encapsulado. El objetivo final de un procesador basado en chiplets es mantener o mejorar el rendimiento mientras se reducen los gastos de producción en comparación con los IC monolíticos tradicionales. La eficacia del diseño de chiplets depende en gran medida de las técnicas de empaquetado, especialmente las utilizadas para interconectar múltiples chiplets, ya que impactan significativamente en el rendimiento general del sistema. Estas tecnologías avanzadas de empaquetado de semiconductores, que incluyen enfoques como 2.5D CI, 3D CI y encapsulado wafer-level de alta densidad, se denominan colectivamente "encapsulado avanzado de semiconductores". Estas técnicas de vanguardia se examinan en detalle en el informe de investigación de IDTechEx titulado "Encapsulado Avanzado de Semiconductores 2022-2032". Facilitan la convergencia de múltiples chiplets, a menudo producidos en nodos de proceso diferentes, en un solo sustrato. Esta convergencia es posible mediante el uso de tamaños compactos de bump, lo que permite densidades de interconexión más altas y capacidades de integración superiores.

Evolución de las Tecnologías de Empaquetado de Semiconductores

Fuente: Informe de IDTechEx "Empaquetado Avanzado de Semiconductores 2022-2032"

Al observar el panorama actual de las tecnologías de empaquetado avanzado de semiconductores en la industria, tomemos el sector de CPU de servidores como ejemplo ilustrativo. Si bien la mayoría de las CPUs de servidor contemporáneas se construyen en torno a diseños monolíticos de System-on-Chip (SoC), han surgido desarrollos notables. En 2021, Intel anunció su próxima CPU de servidor, Sapphire Rapids, que adoptará un enfoque novedoso. Esta CPU de próxima generación se construirá como un módulo de cuatro chips interconectados mediante el puente de interconexión de múltiples dados integrados de Intel (EMIB), lo que representa una solución de empaquetado avanzado de semiconductores 2.5D.

Al mismo tiempo, AMD ha adoptado el poder de las técnicas de encapsulado 3D avanzado de semiconductores para mejorar el rendimiento de las CPUs de servidor. En el caso de su última CPU de servidor, Milan-X (lanzada en marzo de 2022), AMD emplea una estrategia de encapsulado 3D que implica apilar un dado de caché directamente sobre el procesador. Según las afirmaciones de AMD, esta innovación resulta en un aumento notable de la densidad de interconexión (>200x) en comparación con el encapsulado convencional en 2D. Estos avances no se limitan solo a las CPUs; el ámbito del centro de datos también ha sido testigo de la integración de tecnologías avanzadas de encapsulado de semiconductores para otros componentes, como los aceleradores. NVIDIA, un actor clave, ha estado utilizando la tecnología de encapsulado 2.5D de TSMC conocida como Chip on Wafer on Substrate (CoWoS) para sus aceleradores de GPU de alta gama desde 2016.

Un Futuro de Integración Avanzada en el Sector Automotriz y de Cálculo de Alto Rendimiento (HPC)

En el futuro previsible (en un período de 10-15 años), impulsado por los crecientes requisitos de procesamiento y la necesidad de un ancho de banda sustancial con un consumo mínimo de energía, el sector automotriz emulará una trayectoria similar a la del mercado de la nube y la computación de alto rendimiento (HPC). Esta trayectoria implica la integración de diversas propiedades intelectuales (IP) y elementos de silicio a nivel de encapsulado para obtener características esenciales y un rendimiento óptimo. En el contexto de los procesadores de computación de vehículos autónomos (AV), el panorama de encapsulado presenciará la amalgama de múltiples componentes de silicio dentro del mismo paquete, implementando enfoques avanzados en 2.5D y 3D.

Con la creciente demanda de cálculo de alto rendimiento en vehículos y la necesidad de un crecimiento continuo del rendimiento, habrá una rápida evolución en la tecnología que se incorpora a las computadoras automotrices. Tamaños de nodo sub-3nm, diseños de chiplets, una mayor dependencia de la aceleración de IA, encapsulado 2.5D e incluso encapsulado 3D se convertirán en una parte normal de la HPC para tecnologías autónomas en automóviles. Las computadoras han estado en los autos durante décadas, pero las tecnologías que se avecinan harán que un automóvil promedio de hoy parezca tecnología de línea fija en un mundo de teléfonos inteligentes.

Autores: Dr. James Jeffs, Analista Senior de Tecnología en IDTechEx y Dr. Yu-Han Chang, Analista Senior de Tecnología en IDTechEx

Suscríbete a nuestro boletín de noticias