Los modernos circuitos integrados formadores de haces (BFIC) suelen tener múltiples rutas paralelas en un chip con ganancia y fase controlables de forma independiente. Las configuraciones BFIC comunes tienen dos o más de estas rutas RF en chip conectadas a pines que se encuentran en el mismo borde y/o en la misma esquina del paquete IC. La figura 1 muestra un BFIC de 4 entradas y 4 salidas con las cuatro entradas en el mismo borde del paquete del IC y las cuatro salidas en el borde opuesto. Esta arquitectura de dispositivo se utiliza en la familia ADAR3000/ADAR3001/ADAR3006/ADAR3007 de circuitos integrados formadores de haces de banda Ku y Ka de Analog Devices. El BFIC también debe admitir todos los pines digitales, de alimentación y otros pines diversos que se requieren para su funcionamiento.

La disposición relativamente cercana entre pines en el BFIC es consecuencia del gran número de entradas y salidas de RF y su configuración asociada de señal a tierra. El enrutamiento de múltiples líneas de RF de alta precisión desde estos pines tan próximos entre sí a diferentes dispositivos, conectores u otras placas de circuito impreso (PCB) supone un reto. La baja precisión de la impedancia de la línea de transmisión y las transiciones de impedancia deficientes (por ejemplo, en la transición entre dos placas) provocan reflexiones de la señal. Esto reduce la potencia de RF suministrada a la carga y disminuye la ganancia. Una menor ganancia del sistema y una potencia de salida reducida degradan la potencia isotrópica radiada efectiva (EIRP) en los transmisores. Las reflexiones de señal lo suficientemente grandes también pueden causar inestabilidad, especialmente si el diseño del circuito es susceptible a la potencia reflejada de su carga.

Este artículo trata sobre cómo diseñar y fabricar líneas de transmisión PCB RF de alta precisión y transiciones de conectores con una excelente pérdida de retorno que dirigen las señales hacia y desde la PCB a través de las líneas de transmisión que se conectan a BFIC de entrada y salida RF de alto recuento. Aunque se centra en las aplicaciones BFIC y de matriz en fase, el material se aplica igualmente a cualquier diseño de circuito de alta frecuencia en el que sea importante una buena adaptación de impedancia. Se presentarán múltiples técnicas de diseño, pero también se tratará el importante tema del diseño para la fabricación. Tenga en cuenta que este artículo proporciona las dimensiones principalmente en milésimas de pulgada (1000 milésimas de pulgada equivalen a 1 pulgada). Para convertir de milésimas de pulgada a milímetros, multiplique por 0,0254.

Figura 1. Diagrama de bloques anatómico de un chip BFIC de 4 entradas, 4 salidas y 16 canales en paquete BGA; las dimensiones del contorno no están a escala con el paso entre bolas y el diámetro de las bolas.

Fabricación de diversas topologías de líneas de transmisión

Los fabricantes de PCB admiten múltiples topologías populares de líneas de transmisión de RF, incluyendo microcinta, guía de onda coplanar conectada a tierra (GCPW), línea de banda y la menos popular GCPW enterrada (BGCPW), que se asemeja a un híbrido entre GCPW y línea de banda. Aunque la microcinta es relativamente fácil de fabricar, para un funcionamiento por encima de los 6 GHz es menos popular debido a su mayor pérdida de traza y su deficiente supresión de modo.1 Las GCPW, BGCPW y stripline funcionan mejor por encima de los 6 GHz debido a su menor pérdida de radiación y mejor supresión de modo. Las topologías de línea enterrada mejoran el aislamiento, pero son más difíciles de fabricar y requieren vías para conectarse a ellas. Estas vías suelen ser ciegas para minimizar la inductancia parásita, lo que se traduce en un mayor coste de la placa.

La figura 2 muestra una sección transversal de GCPW, GCPW enterrado y línea de banda, así como las geometrías importantes que establecen la impedancia nominal de la línea. Estas son el ancho de la línea (W1/W2/W3), la distancia lateral desde el borde de la línea hasta el plano de tierra adyacente (G1/G2/G3), el espesor de los materiales dieléctricos (T1/T2) y la permitividad relativa de los materiales dieléctricos (εR1 /εR2 ). La figura 2 no muestra el espesor del cobre utilizado para las líneas ni el cercado de tierra necesario. Es necesario tener en cuenta el espesor del cobre, pero se trata de un efecto secundario. El cercado de tierra necesario se tratará en la parte 2. La elección de la topología depende de la pérdida de traza aceptable, la frecuencia, el aislamiento línea a línea necesario, el espacio disponible y el espesor dieléctrico del material de la PCB.

Figura 2. Sección transversal de las topologías GCPW, GCPW enterrada y línea de banda.

Efectos de las tolerancias de fabricación en la impedancia de línea

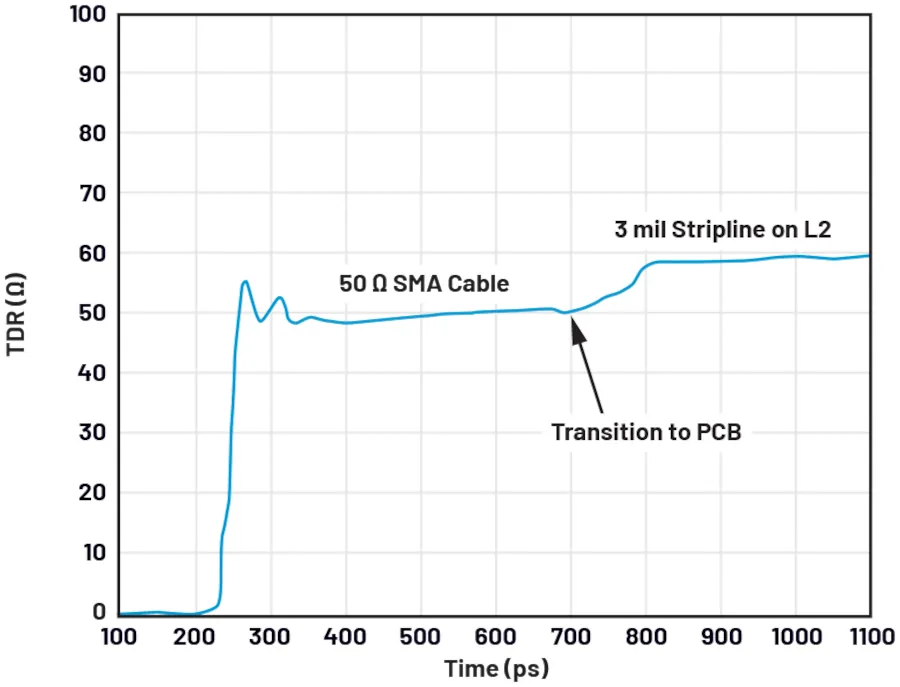

La calidad de las topologías de líneas de RF se ve afectada por las tolerancias de fabricación. Elegir las geometrías óptimas de la línea para minimizar estos efectos es crucial para obtener una impedancia de línea precisa de 50 Ω. La figura 3 muestra un gráfico de reflectometría en el dominio del tiempo (TDR) de una línea de banda de 3 milésimas de pulgada de ancho que se diseñó para 50 Ω, pero que se midió en aproximadamente 60 Ω. Se deseaba un error de no más del ±10 % (45 Ω a 55 Ω) para obtener una pérdida de retorno de 20 dB o mejor.

Tres de las geometrías importantes que hay que tener en cuenta al diseñar la línea son el ancho de la línea, la distancia al suelo lateral y el espesor dieléctrico. Muchos fabricantes de PCB ofrecen anchos mínimos de conductor de hasta 3 milésimas de pulgada (dependiendo del peso del cobre) con una tolerancia de 1 a 2 milésimas de pulgada 2-4.Los fabricantes suelen proporcionar solo cifras típicas de espesor dieléctrico, probablemente porque el espesor final lo determina el fabricante de PCB durante el proceso de laminación de la placa. La distancia lateral al suelo puede variar como resultado de que el plano de tierra no se detenga donde debería. Además, el ancho efectivo de la distancia lateral cambia si varía el ancho de la línea.

Figura 3. Gráfico TDR de una línea de banda de 3 milésimas de pulgada de ancho en la capa 2 de una PCB.

En las topologías de microcinta y línea de banda, las variaciones en el ancho del espacio lateral no deberían afectar a la impedancia de la línea, ya que la distancia lateral al suelo es grande por diseño. Esto hace que todas las líneas de campo vayan al plano de tierra inferior en el caso de la microcinta y a los planos de tierra superior e inferior en el caso de la línea de banda. Sin embargo, el GCPW se ve más afectado por las tolerancias del espacio lateral. Por diseño, la distancia lateral entre el espacio y la tierra es relativamente pequeña y la mayoría de las líneas de campo van al plano de tierra lateral.

La figura 4 muestra la impedancia de línea 5 de un diseño de línea de banda frente a la desviación del ancho de línea con respecto al valor nominal para múltiples anchos de línea. También se muestra la desviación de impedancia que se produce cuando el dieléctrico es un 5 % más grueso que el valor nominal (suponiendo un espesor de cobre de la línea de banda de 0,7 milésimas de pulgada y εR = 3,1). Lo ideal sería que la pendiente de todas las líneas fuera 0 y que no hubiera desplazamiento de la intersección entre las líneas, lo que indicaría que no hay variaciones en la fabricación. Obsérvese que las líneas más anchas tienen una pendiente menor, mientras que las líneas más estrechas tienen una pendiente más pronunciada. Por lo tanto, en la práctica, cuando hay variaciones en la fabricación, es preferible un ancho de línea nominal más amplio. Lamentablemente, con un aumento del espesor dieléctrico del 5 %, el desplazamiento de la impedancia es aproximadamente igual independientemente de los anchos de línea nominales. Esto significa que el fabricante debe cumplir los requisitos de espesor final prensado dentro de una determinada tolerancia para alcanzar la tolerancia de impedancia de línea deseada. La atención se centra en el aumento del espesor dieléctrico (frente a la disminución del espesor) porque se ha observado en muchos lotes de fabricación de placas con diferentes topologías de línea que la impedancia de la línea tiende a ser mayor o igual al objetivo de diseño. Esto lleva a la regla general de diseñar la línea con unos pocos ohmios menos que el objetivo, especialmente cuando el ancho es fino (menos de 5 milésimas de pulgada). Sin embargo, con este enfoque, es posible que sea necesario renunciar a los requisitos de impedancia controlada que normalmente limitan al fabricante de PCB, dependiendo de la diferencia de impedancia. Si se debe utilizar una línea delgada debido a otras consideraciones de diseño, es fundamental tener una gran confianza en el fabricante elegido. La confianza se puede ganar de forma orgánica utilizando un fabricante de diseños anteriores y/o de forma intencionada fabricando placas experimentales con la topología de línea elegida, con múltiples líneas de diferentes anchuras que harían que las líneas tuvieran un diseño de alrededor de 50 Ω. A continuación, sería necesario realizar mediciones para determinar qué anchura de línea se acercaba más a 50 Ω.

Figura 4. Error de impedancia (para 50 Ω) frente a tolerancia de fabricación para anchos de línea de 3, 5, 7 y 10 milésimas de pulgada sobre el espesor dieléctrico nominal y +5 %.

Conexiones dentro de la placa: entrada y salida de señales de la PCB

Las discontinuidades de impedancia de RF entre las líneas de transmisión de RF y los conectores de RF que mueven las señales entre las PCB son tan importantes como la impedancia de línea precisa que se ha comentado anteriormente. Al realizar la transición entre placas, hay dos opciones de interconexión física:

1. Conectores de lanzamiento lateral que se montan lateralmente en el borde de la PCB.

2. Conectores de lanzamiento vertical que se montan verticalmente en la PCB.

Ambos tipos están disponibles en SMA, SMP, SMPM, 2,92 mm y 2,4 mm, por nombrar algunos estándares.

La elección entre el lanzamiento lateral y el lanzamiento vertical dependerá en gran medida del factor de forma del equipo final. Si se utilizan conectores de lanzamiento lateral, la placa de circuito impreso de interconexión se dispondrá lateralmente. Si el sistema se encuentra en un único chasis metálico/disipador de calor, esta disposición puede ser la mejor opción. Si se utilizan conectores de lanzamiento vertical, existe la posibilidad de apilar varias placas en forma de sándwich. Esto puede dar lugar a un factor de forma más compacto, pero también puede obligar a utilizar refrigeración por aire, ya que es poco probable que las placas individuales tengan disipadores de calor. Una combinación de ambos tipos de conectores, una placa con lanzamiento lateral y otra con lanzamiento vertical, hará que las dos placas se conecten ortogonalmente en forma de ranura.

Conectores de lanzamiento lateral frente a conectores de lanzamiento vertical

Los conectores de lanzamiento lateral se utilizan ampliamente. Sin embargo, tienen algunos inconvenientes potenciales que se derivan de su fijación al borde de la placa. Los conectores laterales suelen requerir una traza más larga, en comparación con los conectores verticales, desde el dispositivo hasta el conector. Esto da lugar a un aumento de la pérdida de inserción, la capacitancia parásita y la inductancia. Los conectores laterales también requieren que el plano de tierra superior de la PCB (y preferiblemente el plano de tierra inferior) se extienda hasta el borde de la placa. La mayoría de los fabricantes de PCB solo pueden garantizar una distancia de 2 milésimas de pulgada entre el borde del plano de tierra y el borde de la placa en las ubicaciones de los conectores cuando se utilizan técnicas estándar de fresado/rutear de bordes y retroceso de grabado. Esto se manifiesta como una discontinuidad de impedancia debido a la falta de retorno de tierra en el espacio de 2 milésimas de pulgada (o más) y degrada la pérdida de retorno. Esta discontinuidad se hace más pronunciada a frecuencias más altas.

La figura 5a muestra una transición de conector de borde de PCB con un gran espacio entre el borde de la placa y el plano de tierra, mientras que la figura 5b muestra un gráfico TDR que muestra el pico de impedancia producido por un gran espacio en el conector. A frecuencias más bajas, es posible que el espacio no afecte al rendimiento y podría ser deseable, ya que mantiene el extremo de la frágil línea de transmisión alejado de la fresa que está fresando el borde de la placa. Una solución sencilla consiste en terminar la línea de transmisión 2 milésimas de pulgada antes del borde del plano de tierra, lo que es una distancia suficiente para mantenerla alejada de la fresa (evitando daños) y seguir proporcionando una buena transición para el pin central del conector. Esta técnica se utiliza a menudo en aplicaciones de ondas milimétricas de alta frecuencia.

Figura 5. (a) Vista superior de una transición de conector de borde con un gran espacio entre el borde de la PCB y el plano de tierra de la capa superior y (b) gráfico TDR de una transición deficiente debido a un mal enrutamiento del borde que crea un gran espacio (el segundo pico de lanzamiento del conector se debe a una menor energía reflejada).

Existen un par de opciones para mitigar el espacio entre el plano de tierra y el borde de la placa. La primera es utilizar un revestimiento de borde en las ubicaciones de los conectores en el borde de la placa. Cuando se hace correctamente, esto elimina eficazmente el espacio por completo al aplicar un revestimiento metálico de tierra en el borde vertical de la placa. El revestimiento de borde se conecta a los planos de tierra horizontales superior e inferior existentes y también puede conectarse a los planos de tierra internos si se desea. El revestimiento del borde solo debe estar en las partes de tierra del borde y, por lo tanto, debe haber un espacio entre el revestimiento en las ubicaciones de los conectores donde se encuentra la línea de transmisión. Esto se muestra en la Figura 6.

Figura 6. Corte transversal de una PCB en la ubicación del conector del borde que muestra el recubrimiento adecuado del borde.

El revestimiento del borde presenta algunos inconvenientes derivados de la calidad de su fabricación. Esto puede dar lugar a:

• Un corte redondeado de la fresa circular para eliminar el revestimiento en la línea de transmisión (es deseable mantener el borde de la PCB plano).

• Un fresado inconsistente antes de que se produzca el recubrimiento del borde, lo que provoca problemas de coincidencia de la longitud de la línea de transmisión (es muy importante mantener la misma longitud que las trazas de calibración).

• Un recubrimiento que se extiende desde las ubicaciones de tierra en el borde de la placa y invade el área de la línea de transmisión. El peor caso es que el recubrimiento sea continuo en toda la ubicación del conector, incluyendo donde se encuentra la línea de transmisión, como se muestra en la Figura 7. Esto puede provocar un cortocircuito de la línea de transmisión a tierra.

Figura 7. Ejemplo de recubrimiento del borde que invade desde las ubicaciones de tierra hasta el área de la línea de transmisión (vista lateral de la PCB).

Los dos primeros problemas de calidad son indeseables y degradan el rendimiento de la PCB. Sin embargo, no son catastróficos. El tercer problema de calidad es catastrófico y hace que la PCB sea inutilizable, por lo que requiere una reelaboración mecánica para eliminar el recubrimiento del borde en el área de la línea de transmisión. La única forma viable de garantizar que el recubrimiento de los bordes mantenga una alta calidad es exigir los requisitos de recubrimiento de los bordes en las notas de fabricación de la PCB. Dependiendo de lo estrictos que sean los requisitos, es posible que los fabricantes tengan que volver a fabricar lotes de PCB. O pueden rechazar el trabajo.

El fresado de bordes con láser es otra opción. El fresado de bordes con láser consiste en cortar la placa de su panel con un láser. Esto se puede hacer a lo largo de todo el borde de la placa, pero solo es necesario hacerlo en las ubicaciones de los conectores, con fresado mecánico en el resto del borde de la placa. No todos los fabricantes de PCB ofrecen fresado de bordes con láser. Los proveedores que lo hacen suelen garantizar solo un margen de 1 mil, lo que generalmente solo se puede lograr si la PCB es relativamente delgada. Algunos fabricantes de PCB requieren que la placa tenga un grosor inferior a 14 milésimas de pulgada, mientras que otros pueden ofrecer esta precisión en placas de hasta 40 milésimas de pulgada de grosor. Esto sigue siendo relativamente delgado y plantea la posibilidad de que la placa se deforme, especialmente en el caso de placas más grandes, y normalmente no es lo suficientemente grueso para placas con un alto número de capas.

El revestimiento de los bordes y el fresado láser de los bordes pueden aumentar el coste, la complejidad y el tiempo de fabricación. Si el factor de forma del equipo final permite que las placas se intercalen entre sí (en lugar de conectarse lateralmente), las interconexiones de lanzamiento vertical pueden ser una opción viable.

Interconexiones de lanzamiento vertical

Al no estar unidos al borde de la placa, los conectores de lanzamiento vertical no son susceptibles a los problemas de enrutamiento de bordes descritos anteriormente. En placas simples de un solo dispositivo, los conectores se pueden colocar cerca del dispositivo que se está probando, lo que da como resultado una pérdida de inserción mínima.

Además, la transición a la placa se puede adaptar a la RF para minimizar la discontinuidad de la impedancia. Los proveedores de conectores, como SVMicrowave, crearán una huella personalizada para un diseño de línea y una pila determinados. En la figura 8 se muestra una huella para un conector de lanzamiento vertical SVMicrowave que se conecta a un diseño de línea de banda. Se muestran cuatro capas de PCB con el cercado de vías. El hueco de 30 milésimas de pulgada de diámetro en la capa 3 (L3) es la adaptación para el conector y se muestra en la figura 8c.

Una desventaja de los conectores de lanzamiento vertical es que puede resultar difícil lograr una buena alineación entre el conector y la huella de la placa de circuito impreso. Lo ideal es que el pin central circular del conector se conecte a su almohadilla circular en la placa de circuito impreso y que sus centros estén alineados. Sin embargo, al mirar hacia abajo el conector cuando se monta en el plano de tierra 2D, es posible que se produzca un movimiento de izquierda a derecha y de adelante hacia atrás, lo que puede hacer que el pin central no quede centrado con la almohadilla de la placa de circuito impreso. Los conectores destinados a líneas que discurren por la capa superior tienen un orificio en la parte delantera que puede ser útil para la alineación, especialmente del movimiento de izquierda a derecha (estos conectores con orificio también se han utilizado con éxito con líneas de banda). La tolerancia del tamaño del orificio de montaje debe ser estrecha para que el movimiento excesivo del conector sea mínimo. Si se necesita una alineación exacta, como es el caso de frecuencias >35 GHz, Rosenberger ofrece conectores que se lanzan a 45° con respecto a la placa (frente a los conectores verticales de 90°) y que se pueden alinear manualmente con mucha más facilidad que los conectores verticales. Sin embargo, estos conectores de lanzamiento a 45° son más caros que sus homólogos verticales y de lanzamiento lateral y requieren un espacio mucho mayor en la PCB ( ).

Figura 8. Diseño de la huella del conector vertical personalizado: (a) la tierra superior en la capa 1, (b) la línea de banda en la capa 2, (c) un espacio vacío de 30 milésimas de pulgada en la capa 3 para la adaptación, y (d) un plano de tierra sólido en la capa 4.

Conclusión

La llegada de los circuitos integrados formadores de haces de alta frecuencia y otros circuitos integrados de RF multicanal de alta frecuencia está haciendo que el diseño de PCB sea más complicado. Al abordar estos diseños tan complejos, los diseñadores de PCB deben anticiparse a los posibles problemas de fabricación evitando el uso de trazas de RF muy finas y, en general, diseñando para una impedancia característica ligeramente inferior al valor objetivo de 50 Ω. Al diseñar interconexiones de placa a placa, lo más probable es que se elijan interconexiones de lanzamiento superior o de lanzamiento lateral en función del factor de forma del equipo final. Las interconexiones de lanzamiento superior son menos susceptibles a las limitaciones de fabricación que pueden producirse en el borde de la placa.

En la segunda parte de esta serie de artículos se analizará cómo el aislamiento de la línea de transmisión puede afectar al rendimiento de los circuitos integrados de formadores de haces de alta frecuencia, las diferencias de aislamiento entre las topologías de las líneas de transmisión y cómo elegir la mejor línea de transmisión para una aplicación determinada y la geometría del BFIC.

Referencias

1 John Coonrod. «Comparación entre microcintas y guías de onda coplanares con conexión a tierra». Rogers Corporation.

2«Tolerancias de PCB en la fabricación». MADPCB.

3«Tolerancias». AdvancedPCB.

4«Tolerancias». Imagineering, Inc.

5«Stripline». Microwaves101.

Acerca del autor

Joel Dobler es ingeniero principal de aplicaciones de productos en el Grupo Aeroespacial, de Defensa y Comunicaciones, donde se centra en productos formadores de haces, pero también presta apoyo a moduladores vectoriales y filtros de paso bajo programables. Trabaja para Analog Devices desde 2006, donde presta apoyo a una amplia gama de productos de RF, incluidos detectores logarítmicos y RMS, amplificadores de ganancia variable digitales y analógicos, mezcladores y demoduladores I/Q. Obtuvo su licenciatura en Ingeniería Eléctrica en la Universidad Estatal de Washington en 2005 y su máster en Ingeniería Eléctrica en la Universidad Estatal de Portland en 2007.