Tel.: +34 91 706 56 69

Poema Sinfónico, 27. Esc B. Planta 1 Pta 5

28054 (Madrid - SPAIN)

e-mail: gm2@gm2publicacionestecnicas.com ó consultas@convertronic.net

Tras la rápida expansión experimentada por las opciones de productos de SiC, el siguiente reto de la industria es simplificar el proceso de diseño a los usuarios finales. Los desarrolladores de sistemas de potencia necesitan soluciones integrales que aborden no solo los elementos típicos de diseño de forma individual, sino que también reconozcan la importancia de sus interacciones. Dicho de otra manera, los suministradores de SiC no solo deben demostrar el rendimiento y la robustez de su tecnología de MOSFET de SiC, sino que además deben ayudar a superar los retos del diseño, ofreciendo para ello un encapsulado de potencia de baja inductancia y unos drivers de puertas más sofisticados con el fin de cumplir, proteger y ajustar con precisión los parámetros del sistema. Hay que prestar especial atención a estos tres elementos clave para simplificar la evaluación y el diseño a quienes tratan de aprovechar las revolucionarias mejoras a nivel de sistema que posibilita el SiC.

MOSFET de SiC robustos y resistentes

Se puede afirmar que los MOSFET de SiC constituyen el eslabón más crítico en la cadena de un sistema de potencia. De ahí que deban demostrar su robustez en varios aspectos donde han sido vulnerables. Al igual que los MOSFET de silicio, también se enfrentan al problema de defectos extrínsecos como impurezas, estados de carga y otros defectos del material cerca de la unión óxido-semiconductor, que provocan inestabilidades de diverso tipo en el dispositivo y mecanismos de degradación. Eliminar estos riesgos requiere que los MOSFET de SiC para producción demuestran una tensión de umbral estable, un óxido de puerta fiable, un robusto diodo estructural intrínseco y resistencia frente a avalanchas. Cada atributo se debe validar mediante pruebas de cualificación ya que la estabilidad de los parámetros y la vida útil pueden variar enormemente en función del suministrador.

Para comprobar la estabilidad de la tensión de umbral (Vth) de un MOSFET de SiC, generalmente se aplica una polarización de puerta positiva (p-HTGB) y negativa (n-HTGB) a alta temperatura para someter a estrés a un número significativo de dispositivos desde un punto de vista estadístico y simplemente comparar la Vth antes y después de la prueba de estrés en las muestras. Por ejemplo, se han aplicado p-HTGB y n-HTGB a conjuntos independientes formados por sesenta y cuatro MOSFET de SiC de 1200 V durante 1.000 horas. El cambio medio observado en Vth fue de +59,6 milivoltios tras

p-HTGB y -22,8 milivoltios tras n-HTGB. Con este nivel de estabilidad, los desarrolladores disponen de una tensión de umbral previsible a partir de la cual pueden tomar decisiones de diseño más estrictas y a más largo plazo.

Los óxidos de puerta de alta fiabilidad son primordiales en todas las aplicaciones, especialmente aquellas que requieran una larga vida útil. Para determinar la fiabilidad del óxido de puerta en el MOSFET de SiC se efectuaron medidas de carga hasta ruptura (QBD) en tres conjuntos de MOSFET de SiC de 1200 V. Todos los fallos observados fueron intrínsecos, lo cual indicó un alto nivel de madurez del proceso. Las tasas de fallos en el tiempo (FIT) y de tiempo medio entre fallos (MTTF) se calcularon para un mayor número de dispositivos, en concreto 192. Para p-HTGB, estos valores fueron de 20 y 5.618 años, respectivamente; para n-HTGB, los resultados obtenidos fueron 93 y 1.233 años. Para los usuarios finales estos resultados deberían ser alentadores ya que están en consonancia con los informes de ruptura dieléctrica dependiente del tiempo (TDDB) proporcionados por diversos suministradores.

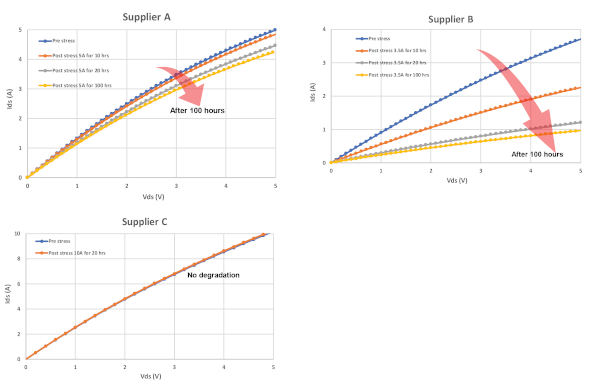

El fenómeno de la degradación bipolar en las uniones p-n de SiC ha sido ampliamente estudiado. En el caso de que se produzca en el diodo estructural de un MOSFET de SiC se observarían incrementos tanto de la resistencia en conducción como de la caída de tensión en el diodo durante la conmutación de corriente (que se manifiesta por la tendencia a la baja de las características de salida del tercer cuadrante). Afortunadamente los materiales de los MOSFET de SiC han evolucionado y la densidad de los defectos en los cristales preexistentes ha disminuido en los materiales de producción. Aun así, es preciso evaluar los MOSFET de SiC de cada suministrador. La Ohio State University comparó recientemente la degradación del diodo estructural tras 100 horas de estrés a la máxima corriente nominal (VGS = -5 V) en MOSFET de SiC de 1200 V de varios suministradores y observó disparidades sustanciales de la resistencia en conducción tras la fase de estrés. Tan solo el Suministrador C demostró la ausencia de degradación (Figura 1). Los datos complementarios del tercer cuadrante en los mismos dispositivos corroboraron la presencia (o ausencia, para el Suministrador C) de degradación del diodo estructural.

Figura 1. Los datos del tercer cuadrante muestran que el MOSFET de SiC del Suministrador C fue el único que no sufrió una degradación del diodo estructural. Fuente: Dr. Anant Agarwal y Dr. Minseok Kang, Ohio State University.

Figura 1. Los datos del tercer cuadrante muestran que el MOSFET de SiC del Suministrador C fue el único que no sufrió una degradación del diodo estructural. Fuente: Dr. Anant Agarwal y Dr. Minseok Kang, Ohio State University.

Otro parámetro importante es la resistencia frente a avalanchas, que se lleva a cabo mediante conmutación inductiva desbloqueada (unclamped inductive switching, UIS). El MOSFET recibe una sobrecarga eléctrica mientras está en OFF, lo cual fuerza a la corriente a generar una avalancha en la periferia de la pastilla de semiconductor (die) ya que el canal MOS no se enriquece.

Esto difiere de una prueba de resistencia a cortocircuitos, en la que el MOSFET se encuentra en ON y la corriente se distribuye de manera más uniforme por toda el área activa del dispositivo. Para imitar mejor las condiciones reales de funcionamiento, los MOSFET de SiC se someten a pulsos repetitivos de UIS (R-UIS); la estabilidad de los parámetros y la integridad del óxido se comparan antes y después de 100.000 pulsos repetitivos a dos tercios de la corriente nominal (según MIL-STD-750). VBR, Vth y VF del diodo estructural no se van afectadas por R-UIS, lo que indica su excelente resistencia frente a avalanchas.

Encapsulado de potencia de baja inductancia

Una vez establecida la confianza en el MOSFET de SiC, la siguiente pieza de un sistema total de SiC es un encapsulado de potencia optimizado. Un encapsulado de módulo multichip efectivo debería permitir que los diseñadores aprovechan las ventajas del SiC en lugar de limitarlas.

Hay que tener en cuenta numerosos requisitos. Dado que la pastilla de semiconductor del MOSFET de SiC es pequeña en términos comparativos, muchos de ellos se deben conectar en paralelo para obtener una baja resistencia en conducción. Además, la pastilla de semiconductor del MOSFET en paralelo debe conmutar de forma sincronizada y compartir la corriente de modo uniforme, lo cual significa garantizar su simetría y su baja inductancia en los esquemas de interconexión de la pastilla de semiconductor.

Un ejemplo de ello es el encapsulado SP6LI de Microchip, que solo añade 2,9 nH de inductancia parásita en el lazo de alimentación, frente los más de 20 nH de inductancia parásita en los encapsulados de módulos estándar. La inductancia del lazo de alimentación se reduce estableciendo las conexiones del enlace de CC en barras colectoras configuradas en línea plana. Las conexiones del sustrato se distribuyen simétricamente y están lo más cerca posible de la pastilla de semiconductor. Respecto al lazo puerta-fuente, se utilizan ranuras de resistencia de puerta en serie independientes para cada uno de los espacios disponibles en la pastilla de semiconductor en las posiciones del conmutador de alto y bajo potencial (high/low side) con el fin de optimizar la sincronización y el reparto de corriente. Las resistencias de puerta independientes reducen la inductancia parásita introducida en el lazo puerta-fuente, ofrecen protección frente a disparos catastróficos y minimizan las pérdidas de conmutación.

Tecnología del driver de puerta inteligente y flexible

Un tercer elemento necesario para un sistema total de SiC es el control. Una vez más, la capacidad de los MOSFET de SiC de conmutar con rapidez provoca que un sistema no optimizado corra el riesgo de fallar debido a las EMI y a picos de transitorios de tensión. Hace falta una nueva tecnología del driver de la puerta que permita al diseñador manipular la dinámica de conmutación y lograr un óptimo equilibrio. Además, el driver de la puerta debe proporcionar rapidez de detección y respuesta a picos de señal dado que los MOSFET de SiC se caracterizan por resistir menos tiempo que la mayoría de los IGBT de silicio.

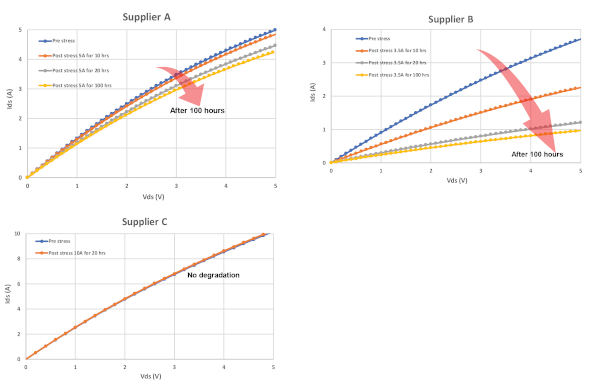

Una técnica patentada que se denomina conmutación aumentada ha hecho posible que las soluciones más avanzadas de driver de puerta digital se detengan a una VGS intermedia y establecida por el usuario con la duración deseada para descargar la capacidad de Miller antes de pasar a VGS (ver Figura 2) en OFF. Esto contrasta con los métodos tradicionales que llevan VGS directamente de ON a OFF, por lo que no ofrecen al diseñador ninguna ruta de escape para esquivar otros problemas menos evitables del sistema, como la inductancia parásita del cable utilizado para conectar la carga. De hecho, se puede lograr un extraordinario equilibrio entre sobretensiones y eficiencia introduciendo pequeñas modificaciones en el perfil de conmutación aumentada (niveles de VGS y tiempo de permanencia).

Figura 2: Un driver de puerta digital que utiliza el método de conmutación aumentada facilita mucho la identificación de los puntos de diseño óptimo y su valoración.

Figura 2: Un driver de puerta digital que utiliza el método de conmutación aumentada facilita mucho la identificación de los puntos de diseño óptimo y su valoración.

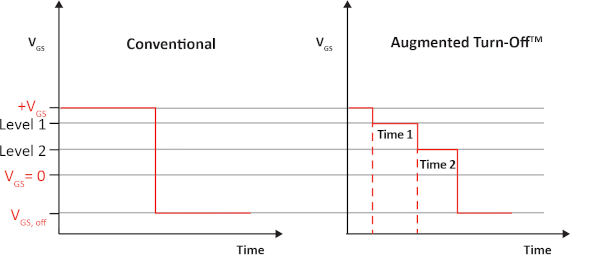

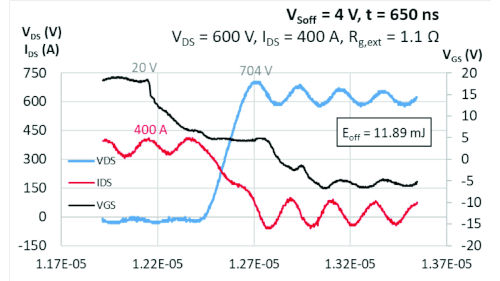

La Figura 3 muestra formas de onda de desconexión mediante el uso de dos perfiles de conmutación aumentada y un módulo MOSFET de SiC de 1200 V en un encapsulado D3 (106 mm x 62 mm x 31 mm). Se puede observar que al seleccionar una VGS intermedia más baja se reducen las pérdidas de conmutación cuando la eficiencia es prioritaria, mientras que una VGS más elevada atenúa los picos de VDS y suaviza las oscilaciones de las tres formas de onda.  Gracias a la herramienta de configuración de software suministrada se pueden establecer con precisión los ajustes del driver de la puerta en todas las etapas de desarrollo con solo pulsar el ratón, a diferencia de las horas ocupadas en manejar un soldador.

Gracias a la herramienta de configuración de software suministrada se pueden establecer con precisión los ajustes del driver de la puerta en todas las etapas de desarrollo con solo pulsar el ratón, a diferencia de las horas ocupadas en manejar un soldador.

Figura 3. Formas de onda de desconexión que muestran el efecto de la conmutación aumentada sobre un módulo de MOSFET de SiC.

Los drivers de puerta digitales también pueden mejorar el nivel de inteligencia. Por ejemplo, se pueden utilizar para obtener un perfil de desconexión totalmente diferente en el caso de que produzca un fallo con el fin de garantizar mejor un funcionamiento seguro. La incorporación de métodos de conmutación aumentada a la protección frente a cortocircuitos refuerza el uso de una baja Rg, además de guiar el MOSFET a través de una transición más suave y controlada a OFF con una menor probabilidad de que se produzca una avalancha. Otras funciones aún más configurables son medidas de diagnóstico en tiempo real como la monitorización de la tensión y la temperatura del enlace de CC.

A medida que la electrónica de potencia evoluciona de los IGBT de silicio a los MOSFET de SiC se basan más en unos suministradores de componentes que proporcionen los elementos críticos que necesitan para crear soluciones como sistemas totales. Esto se concreta en un MOSFET de SiC con una robustez demostrada, un encapsulado de potencia de muy baja inductancia y una nueva clase de drivers de puerta inteligentes diseñados para facilitar la optimización. Todos ellos son imprescindibles para agilizar el diseño del SiC desde su evaluación inicial hasta su instalación en campo.

Autor: Kevin Speer, Microchip Technology

Suscripción papel: 180,00.- € (IVA inc.)

Suscripción PDF: 60,00.- € (IVA inc)

Power Integrations ha presentado un nuevo miembro de su familia InnoMux™-2 de circuitos integrados de fuente de alimentación offline de una sola...

Melexis presenta el MLX92235, un conmutador de efecto Hall de potencia ultrabaja con las mejores tolerancias de su clase para una frecuencia de...

Mecter se complace en anunciar el lanzamiento de los nuevos circuitos integrados periféricos de teclas táctiles de Holtek, la serie BS21xC-x. Estos...

La rápida transición hacia medios de transporte climáticamente neutros y energéticamente eficientes supone una contribución importante a un futuro...

Suscríbete a nuestro boletín de noticias