Implementación de un controlador de motor flexible y optimizado para el sistema en una FPGA

Los motores pueden representar más de dos tercios del consumo de energía en la línea de producción de una fábrica. De ahí que sea fundamental para el balance de la fábrica que el funcionamiento del equipamiento que incorpora motores se optimice para reducir el consumo de energía. El uso de accionamientos de velocidad variable (AVV) en sistemas que incorporen motores ha aportado notables eficiencias directamente relacionadas con el ahorro de energía, pero exigen complejos algoritmos de control.

Los motores pueden representar más de dos tercios del consumo de energía en la línea de producción de una fábrica. De ahí que sea fundamental para el balance de la fábrica que el funcionamiento del equipamiento que incorpora motores se optimice para reducir el consumo de energía. El uso de accionamientos de velocidad variable (AVV) en sistemas que incorporen motores ha aportado notables eficiencias directamente relacionadas con el ahorro de energía, pero exigen complejos algoritmos de control.

Es habitual que un AVV utilice microcontroladores o procesadores de señal digital disponibles comercialmente para implementar el procesado y los lazos de control, que pueden monitorizar la carga y controlar directamente el par motor, la velocidad, la posición y otros aspectos relacionados con el accionamiento. No obstante, estos dispositivos se ven restringidos por su falta de escalabilidad y de prestaciones para procesar unos algoritmos cada vez más complejos en el soporte de dispositivos con ejes múltiples. En la actualidad los controladores de motores han de instalarse en red como soporte a la automatización industrial, pero los microcontroladores o los procesadores de señal digital carecen de la flexibilidad necesaria para cumplir una amplia variedad de estándares de red industriales que existen en la actualidad.

Los diseñadores están dedicando su atención ahora a las FPGA para los sistemas AVV de próxima generación debido a su flexibilidad inherente y a sus prestaciones, así como las ventajas en cuanto a integración y flujo de diseño. No obstante, muchos ingenieros de control de motores están especializados en software o algoritmos para DSP, y no son diseñadores de RTL que estén familiarizados con el diseño basado en FPGA.

Los diseñadores están dedicando su atención ahora a las FPGA para los sistemas AVV de próxima generación debido a su flexibilidad inherente y a sus prestaciones, así como las ventajas en cuanto a integración y flujo de diseño. No obstante, muchos ingenieros de control de motores están especializados en software o algoritmos para DSP, y no son diseñadores de RTL que estén familiarizados con el diseño basado en FPGA.

Para superar este desajuste ocasionado por la necesidad de especialización se han utilizado técnicas de diseño basadas en modelo como MATLAB/Simulink para un mejor modelado de estos algoritmos. Junto con la herramientas de diseño basadas en bloques, como el conjunto de bloques DSP Builder Advanced de Altera, los diseñadores de DSP están en condiciones de trabajar con un entorno MATLAB conocido y generar un RTL optimizado automáticamente. DSP Builder puede compartir en el tiempo operadores lógicos como multiplicadores y sumadores, y es compatible con la aritmética de coma flotante y de coma fija directamente en hardware. Los bloques DSP de precisión variable en la FPGA pueden manejar el algoritmo del motor de sincronización precisa con su DSP de coma fija y flotante y pueden implementar con facilidad operaciones de cálculo intensivo como el control orientado a campo (Field Oriented Control, FOC).

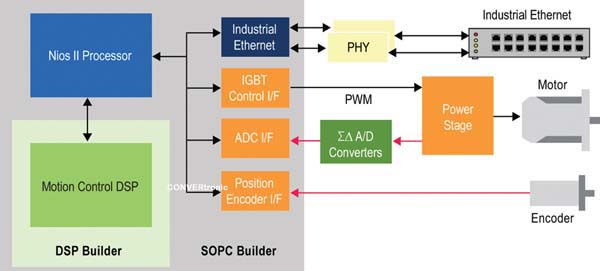

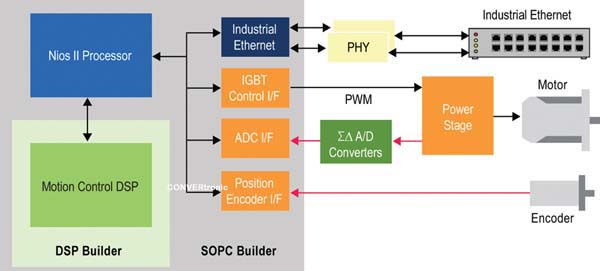

Otra ventaja inherente de una FPGA es que puede integrar la mayor parte de los bloques funcionales de un sistema de control de motores debido a su capacidad de procesar los lazos de control y ofrecer soporte a la gestión en paralelo. Procesadores embebidos como el Nios® II (procesador de software RISC de 32 bit) de Altera® pueden controlar las diversas E/S, así como ofrecer filtrado y conectividad a sensores o dispositivos externos con cualquier estándar de interface digital; por ejemplo, convertidores A/D sigma delta, BISS, ENDAT o codificadores Hyperface, etc. Con un procesador Nios II y un Ethernet MAC a medida es incluso posible implementar un protocolo Ethernet Industrial determinista como EtherCAT o PROFINET. Dado que la FPGA es programable es posible reconfigurar el dispositivo e implementar el soporte para cualquier interface de sensor o estándar de Ethernet industrial sin cambiar el hardware físico. Esta flexibilidad es una ventaja fundamental que aporta el uso de dispositivos FPGA.

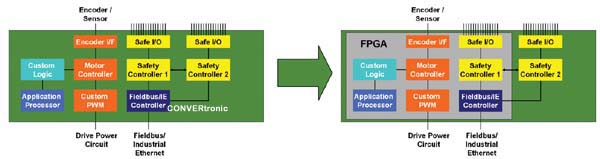

La capacidad que tiene una FPGA de ofrecer soporte a cualquier estándar de Ethernet industrial (o bus de campo serie) también significa que los desarrolladores pueden integrar fácilmente cualquier estándar o pila de protocolo de seguridad en el accionamiento. Altera anunció recientemente la disponibilidad de un paquete de datos de seguridad para sus dispositivos FPGA y herramientas de desarrollo. Éste permite que los desarrolladores integren la funcionalidad relacionada con la seguridad en la misma FPGA que el controlador de accionamiento, disminuyendo así aún más los costes. Con la precertificación del flujo de desarrollo con FPGA, las herramientas de desarrollo y los datos de fiabilidad del dispositivo se reduce notablemente el tiempo de desarrollo y de homologación de seguridad.

En el sistema mostrado en la Figura 2 puede observarse que la sección de seguridad del sistema se implementa por medio de dos controladores de seguridad; esta redundancia existe como protección frente a fallos en la seguridad del sistema. Al comparar las salidas de cada controlador de seguridad se detectará cualquier fallo en un controlador y el sistema podrá ejecutar un apagado de seguridad apropiado. El segundo controlador de seguridad se puede implementar en otra FPGA o en un microcontrolador.

En el sistema mostrado en la Figura 2 puede observarse que la sección de seguridad del sistema se implementa por medio de dos controladores de seguridad; esta redundancia existe como protección frente a fallos en la seguridad del sistema. Al comparar las salidas de cada controlador de seguridad se detectará cualquier fallo en un controlador y el sistema podrá ejecutar un apagado de seguridad apropiado. El segundo controlador de seguridad se puede implementar en otra FPGA o en un microcontrolador.

Ventajas de la FPGA para implementar algoritmos DSP

Las FPGA aportan numerosas ventajas en cuanto a prestaciones, como:

1. Mayor velocidad de funcionamiento y de procesado gracias al paralelismo del hardware de la FPGA y a la escalabilidad a dispositivos de mayor tamaño si es necesario.

2. El menor tiempo de espera debido a la potencial aceleración del hardware de las tareas anteriormente implementadas en software y el interface directo entre el algoritmo del lazo de control y sus interfaces a periféricos (convertidor A/D, PWM, codificador de posición, etc.) mediante la integración en la misma FPGA.

3. Tiempo de espera invariable de algoritmos implementados en hardware. Los tiempos de espera de la implementación en software pueden ser difíciles de prever y pueden ocasionar problemas en tiempo real si no se controlan bien.

4. La síntesis de diseño de alto nivel de Simulink directamente a una implementación en FPGA utilizando DSP Builder no necesita conocimientos avanzados sobre HDL por parte del diseñador del algoritmo.

- La utilización de la función de desdoblamiento permite compensar el tiempo de espera, la velocidad de manejo y la asignación de recursos.

- El soporte a cálculos aritméticos de coma flotante y fija de precisión variable permite optimizar el algoritmo.

raslado del código existente en ‘C’ a una plataforma FPGA

raslado del código existente en ‘C’ a una plataforma FPGA

Los diseñadores pueden migrar aplicaciones a las FPGA utilizando el código ‘C’ existente una vez trasladado a un procesador embebido Nios II. El código se puede perfilar para los cuellos de botella con el uso intensivo del procesador o las tareas en tiempo real descargadas en la FPGA, liberando así al procesador para que asuma otras tareas. Los diseñadores pueden descargar las funciones mediante la creación de instrucciones a medida basadas en RTL escritas a mano o generar aceleradores de hardware DSP mediante DSP Builder.

Para los nuevos diseños, los diseñadores pueden utilizar Simulink desde un principio para modelar el sistema completo con bloques divididos entre software, aceleradores de hardware DSP o IP RTL a medida (interfaces de periféricos u otros).

Conjunto de bloques avanzado de DSP Builder

El conjunto de bloques avanzado de DSP Builder añade bibliotecas especializadas de Simulink al entorno de diseño MATLAB que permite a los diseñadores la implementación de diseños DSP de forma rápida y sencilla. El conjunto de bloques avanzado se basa en una tecnología de síntesis de alto nivel que optimiza la lista de interconexiones (netlist) sin límite de duración, hardware segmentado para la FPGA objetivo con la velocidad de reloj requerida. DSP Builder describe el hardware como VHDL, con scripts que se integran en el flujo de software de Quartus® II y el simulador ModelSim.

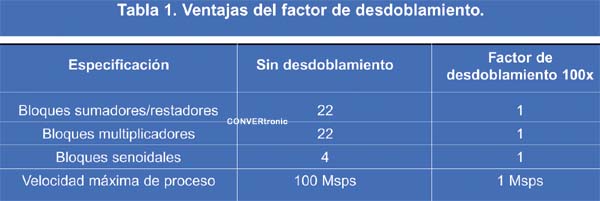

Cuando la velocidad de reloj del sistema es más rápida que la velocidad de los datos o la velocidad de muestreo, un bloque de hardware como un multiplicador puede reprocesar potencialmente múltiples puntos de datos. DSP Builder describe la proporción entre la velocidad del reloj y la velocidad de muestro como “factor de desdoblamiento”. Cuando los diseñadores permiten el desdoblamiento en DSP Builder, existen múltiples puntos de datos que pueden acceder al bloque de hardware compartido, lo cual da como resultado el ahorro de recursos.

Ejemplo típico de control de un motor, pruebas y resultados

Ejemplo típico de control de un motor, pruebas y resultados

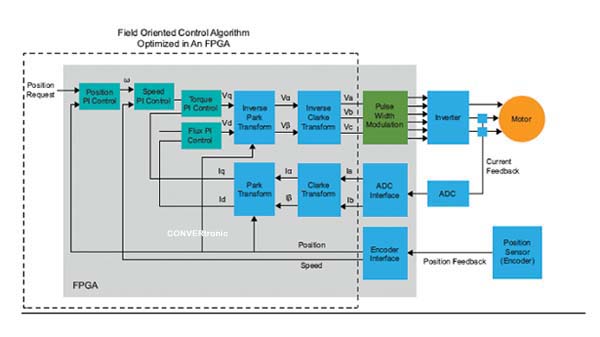

El control orientado a campo (FOC) debe ser capaz de controlar una corriente trifásica senoidal del motor en tiempo real con el fin de crear un diagrama de flujo magnético en suave rotación, donde la frecuencia de rotación corresponde a la frecuencia de las ondas senoidales.

La técnica controla la amplitud del vector de corriente a 90 grados respecto al eje del flujo magnético del rotor (corriente de ”cuadratura”) para

controlar el par mantener el componente de corriente “directa” (0 grados) a cero.

Esta solución también incluye los lazos de control proporcional-integral (PI) de posición y velocidad para permitir el control de la velocidad y el ángulo del rotor. La IP de interface necesaria para completar el diseño mostrado en la Figura 1 se puede obtener fácilmente utilizando la herramienta SOPC Builder de Altera.

En un controlador típico de FOC el software muestrea las entradas a 10-100 ksps y la velocidad del reloj de la FPGA es de 50-100 MHz. A 100 ksps se debe procesar una nueva muestra en menos de 10 µs. Mantener constante este tiempo de espera y al mínimo nivel es beneficioso para las prestaciones del algoritmo de control.

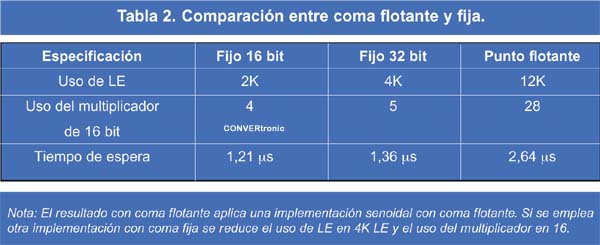

Una vez modelado el algoritmo en Simulink mediante coma flotante de precisión sencilla y con las prestaciones previstas, se genera el hardware para crear la lista de interconexiones VHDL para la FPGA escogida utilizando una velocidad de reloj objetivo de 100 MHz. DSP Builder indica directamente el tiempo de espera del algoritmo obtenido junto con una estimación de los recursos utilizados. Para obtener la utilización precisa de los recursos el diseño se compila a continuación con el software Quartus II.

Una vez modelado el algoritmo en Simulink mediante coma flotante de precisión sencilla y con las prestaciones previstas, se genera el hardware para crear la lista de interconexiones VHDL para la FPGA escogida utilizando una velocidad de reloj objetivo de 100 MHz. DSP Builder indica directamente el tiempo de espera del algoritmo obtenido junto con una estimación de los recursos utilizados. Para obtener la utilización precisa de los recursos el diseño se compila a continuación con el software Quartus II.

Un diseño de este tipo resulta adecuado para su implementación con coma fija, si bien la coma flotante puede aportar numerosas ventajas a los diseñadores:

Evita la sobrecarga de cálculos aritméticos y los problemas de escalado, reduciendo así el tiempo de desarrollo.

Superiores prestaciones gracias a su mayor estabilidad numérica inherente.

Respuestas del lazo de control potencialmente más rápidas debido al elevado rango dinámico.

Las FPGA y herramientas de desarrollo de Altera pueden ofrecer soporte a soluciones de coma fija y flotante.

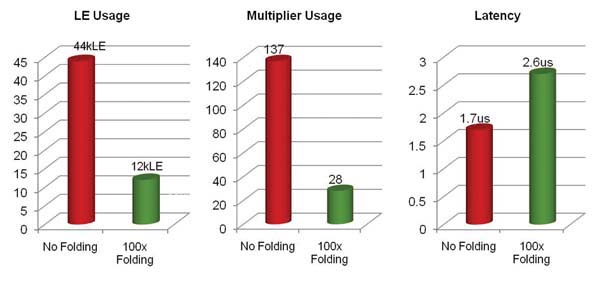

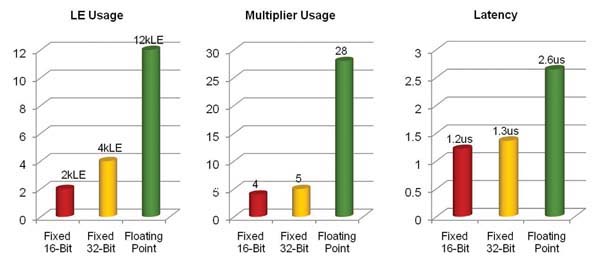

Por defecto, DSP Builder crea una representación totalmente segmentada que puede aceptar nuevos valores de entrada en cada ciclo de reloj. Los diseñadores comparan el resultado obtenido con esta configuración respecto a una configuración con desdoblamiento (ver Figura 3). Los diseñadores realizan la comparación con el mismo algoritmo implementado en coma fija y flotante (ver Figura 4).

Por defecto, DSP Builder crea una representación totalmente segmentada que puede aceptar nuevos valores de entrada en cada ciclo de reloj. Los diseñadores comparan el resultado obtenido con esta configuración respecto a una configuración con desdoblamiento (ver Figura 3). Los diseñadores realizan la comparación con el mismo algoritmo implementado en coma fija y flotante (ver Figura 4).

Los resultados mostrados a continuación demuestran cómo el desdoblamiento ha reducido notablemente el recuento del operador, lo cual permite utilizar un dispositivo Cyclone IV mucho más pequeño con un tiempo de espera mayor pero que siga siendo aceptable para el algoritmo. La velocidad del lazo de control es la suma del tiempo de espera del algoritmo y el tiempo de establecimiento. En 5 microsegundos se obtienen 200k lazos o salidas PWM por segundo, dentro por tanto de la especificación exigida.

Resumen de resultados

1. Con desdoblamiento:

- Reduce el uso de elementos lógicos (LE) y del multiplicador, lo cual permite recurrir a una FPGA muchomás pequeña.

- Incrementa el tiempo de espera pero sigue siendo aceptable para el algoritmo.

- Reduce la velocidad de proceso a 1Msps, que sigue siendo 10 veces más rápido que los 100ksps necesarios para FOC.

- Permite que la solución procese hasta 10 canales del algoritmo FOC en tiempo real.

2. La coma flotante y fija de 32 bit utilizan los recursos de forma similar pero el tiempo de espera para coma fija es casi la mitad. Sin desdoblamiento existe una diferencia mucho mayor entre el uso de los recursos con coma flotante y fija.

3. Al reducir la precisión a 16 bit se reducen los recursos necesarios debido a la ruta de datos más estrecha

Resumen

Los actuales microcontroladores y procesadores de señal digital se están llevando más allá del alcance de sus prestaciones para los controladores de movimiento de próxima generación. Las FPGA ofrecen la plataforma perfecta para el control de movimiento ya que aportan:

- Flexibilidad para integrar toda la funcionalidad en un solo dispositivo.

- Flujos de desarrollo, herramientas e IP homologados para seguridad, así como datos de fiabilidad del dispositivo.

- Prestaciones escalables para procesar múltiples canales y ofrecer soporte a coma flotante de alta precisión.

- Acceso a procesadores embebidos, redes e IP de interface para periféricos y soluciones de sistema que permiten una integración rápida y sencilla del sistema.

Son muchos los ingenieros de diseño que no están familiarizados con el uso de la FPGA en aplicaciones DSP, de ahí que sea importante suministrar herramientas que puedan aumentar la eficiencia y reducir el tiempo de desarrollo. Altera ha desarrollado una serie de herramientas, como SOPC Builder y DSP Builder, que permiten a los usuarios aprovechar los flujos de desarrollo de DSP convencionales y generar rápidamente sus sistemas de control de motores de próxima generación.

Autor:

Kevin Smith, Design Engineer, Senior MTS, Altera.

Articulos Electrónica Relacionados

- Conectores Amphenol Industrial... Mouser Electronics, Inc., tiene disponible el sistema de conexión de la serie Amphe-PD de Amphenol Industrial. Diseñados para conectar terminacion...

- Transmisión serie 610X con mot... La serie 610X, diseñada y desarrollada por Bonfiglioli, ha sido creada para retroexcavadoras híbridas. La serie 610X es un accionamiento operado h...

- Controladores de arranque híbr... Phoenix Contact presenta dos variantes interconectables con interfaz I/O Link en la gama de controladores de arranque híbrido CONTACTRON.Estas permiten u...

- Elegir un relé de potencia par... La elección de relés para aplicaciones industriales exige una cierta consideración. Los criterios más habituales para decidirse por uno u otro van desde la revi...

- Relés de potencia compactos de... Omron Electronic Components Europe ha lanzado dos relés miniatura de potencia, caracterizados por niveles excepcionales de duración y prestaciones...

- Relé MOSFET compacto sin patil... Este nuevo relé MOSFET se caracteriza por su elevada corriente nominal (200V 0,35A) y el alto rango de su temperatura ambiente de funcionamiento en un formato d...

- Motor brushless maxon ECX PRIM... Los motores sin escobillas ECX PRIME son muy potentes, tienen rotores de 4 polos y un bobi-nado sin hierro. En el nuevo motor brushless ECX PRIME 6 M HP, la tec...

- La evolución del USB, el conec... La interfaz USB ha cambiado muchísimo desde que se empezó a usar en 1996. En los últimos veintiséis años, su formato ha experimentado muchas mejoras. La velocid...

- CU250S-2: El control con Encod... Las unidades de control CU250S-2 complementan las ya existentes a través de la funcionalidad de un optimizado control vectorial de lazo cerrado (evaluación de u...

- Relé CC de alta capacidad aume... Omron Electronic Components Europe ha presentado un nuevo relé CC de alta capacidad para sistemas de almacenamiento de electricidad (ESS, por sus siglas en ingl...

- Tact Switch SKSG SKPS y SKSN d... RC Microelectrónica, distribuidor para España y Portugal de Alps Alpine Co, distribuye los nuevos modelos de Tact Switch desarrollados para la marca, que aporta...

- Conectores Micro-D y zócalos p... Cinch Connectivity Solutions ha presentado sus Micro-D Dura-Con™ Space Grade. Fabricada con precisión y diseñada para entornos exigentes, esta nueva línea de pr...