Tel.: +34 91 706 56 69

Poema Sinfónico, 27. Esc B. Planta 1 Pta 5

28054 (Madrid - SPAIN)

e-mail: gm2@gm2publicacionestecnicas.com ó consultas@convertronic.net

El mercado actual, caracterizado por su elevada competitividad, está provocando que los diseñadores de sistemas embebidos reexaminen su proceso de diseño y desarrollo. La mayor complejidad del sistema y el aumento de sus prestaciones, junto con las limitaciones impuestas sobre el consumo de energía y el espacio, fuerzan los límites de los métodos convencionales.

El mercado actual, caracterizado por su elevada competitividad, está provocando que los diseñadores de sistemas embebidos reexaminen su proceso de diseño y desarrollo. La mayor complejidad del sistema y el aumento de sus prestaciones, junto con las limitaciones impuestas sobre el consumo de energía y el espacio, fuerzan los límites de los métodos convencionales.

Al mismo tiempo, la evolución de los estándares, los mercados emergentes y la variación de las tendencias exigen mucha más agilidad y capacidad de respuesta durante el proceso de diseño. Los diseñadores no solo necesitan crear sistemas mucho más complejos, sino que también necesitan ser capaces de obtener con rapidez diseños nuevos o derivados.

Ante semejante nivel de exigencia sobre los equipos de diseño, lo lógico debería ser potenciar el tiempo de desarrollo y los recursos, pero en la práctica está ocurriendo lo contrario. Las ventanas más estrechas de comercialización les exigen producir sistemas más avanzados y ágiles en mucho menos tiempo. Para complicar aún más las cosas, los recortes presupuestarios están obligando a muchos equipos de diseño a reducir su dotación, en lugar de aumentarla. Una manera nueva y más eficiente de ofrecer rápidamente productos adaptables, dotados de numerosas funciones y de altas prestaciones, es la clave para su éxito en el futuro.

Surge una nueva solución

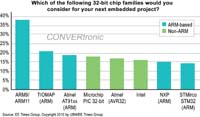

Un desarrollo del mercado que resulta verdaderamente ventajoso para los diseñadores es la aparición del procesador ARM como plataforma dominante para los sistemas embebidos. Hace tan sólo unos años, el mercado de procesadores estaba enormemente fragmentado, con los procesadores PowerPC, RISC, MIPS y SPARC tratando de ganar un amplio nivel de adopción. El mercado ha madurado y muchos clientes han adoptado el procesador ARM como estándar de facto (figura 1) para aplicaciones embebidas. Como resultado de ello, ha crecido el número de soluciones basadas en ARM, desde productos estándar hasta núcleos de IP de software ARM, pasando por IP de hardware para su implantación en lógica programable y ASIC.

Aun así, las opciones de implementación que ofrecen los sistemas embebidos se quedan cortos o apenas cumplen los requisitos de diseño modernos. La implementación de las soluciones multichip resulta relativamente sencilla, pero son costosas y a menudo carecen de la flexibilidad y de la relación prestaciones/ consumo que necesitan los diseñadores. También la implementación de soluciones monochip que emplean núcleos de procesador de software resulta relativamente sencilla, pero sus prestaciones son limitadas. En el otro extremo del espectro, los SoC en ASIC con núcleos ARM de hardware incorporados ofrecen unos excelentes niveles de consumo, prestaciones y optimización, pero su comercialización es lenta debido a sus tiempos de desarrollo, son inflexibles y resultan demasiado caros para la inmensa mayoría de aplicaciones.

Para ser competitivos, los desarrolladores de sistemas embebidos necesitan una opción que les permita desarrollar productos muy diferenciados con niveles mucho más altos de flexibilidad y eficiencia.

La implementación basada en FPGA monochip, con su bajo coste y rápido plazo de comercialización, ofrece una alternativa atractiva de manera intuitiva a las opciones multichip y de SoC en ASIC. De hecho, durante la pasada década hemos sido testigos de un continuo auge del uso de procesadores embebidos en FPGA (figura 2). Sin embargo, no todas las soluciones basadas en FPGA resultan adecuadas para las exigentes demandas actuales. Tradicionalmente, los sistemas ARM basados en FPGA se han implementado recurriendo a núcleos ARM de “soft” basados en HDL. Este método supone una opción viable para sistemas sin fuertes restricciones en cuanto a densidad, consumo o prestaciones, pero quizá no cubra las necesidades de sistemas más competitivos. Para un creciente número de sistemas, la combinación de un núcleo ARM de hardware altamente optimizado sobre una plataforma FPGA ofrece una solución superior.

La implementación basada en FPGA monochip, con su bajo coste y rápido plazo de comercialización, ofrece una alternativa atractiva de manera intuitiva a las opciones multichip y de SoC en ASIC. De hecho, durante la pasada década hemos sido testigos de un continuo auge del uso de procesadores embebidos en FPGA (figura 2). Sin embargo, no todas las soluciones basadas en FPGA resultan adecuadas para las exigentes demandas actuales. Tradicionalmente, los sistemas ARM basados en FPGA se han implementado recurriendo a núcleos ARM de “soft” basados en HDL. Este método supone una opción viable para sistemas sin fuertes restricciones en cuanto a densidad, consumo o prestaciones, pero quizá no cubra las necesidades de sistemas más competitivos. Para un creciente número de sistemas, la combinación de un núcleo ARM de hardware altamente optimizado sobre una plataforma FPGA ofrece una solución superior.

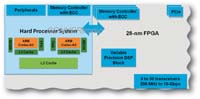

Gracias a los avances más recientes en la tecnología de FPGA de suministradores como Altera ha surgido este nuevo tipo de dispositivo SoC, que ofrece la capacidad deseada por aplicaciones exigentes de sistemas embebidos. Estas FPGA con SoC basado en ARM combinan un procesador de ARM de hardware, controladores de memoria, periféricos y una estructura de FPGA personalizable en un solo SoC.

La FPGA con SoC basado en ARM (como la mostrada en la figura 3) se acopla perfectamente a un sistema procesador de “hard” (HPS) con FPGA integrada. El HPS, que incluye el procesador ARM de doble núcleo, controlador de memoria multipuerto y múltiples elementos periféricos, ofrece un rendimiento de hasta 4.000 MIPS (Dhrystones 2.1 benchmark) por menos de 1,8 W. Estos bloques de IP de hardware ofrecen unas altas prestaciones junto con uno bajo consumo de energía y bajo coste, al tiempo que liberan recursos lógicos para la diferenciación del producto. El diseñador puede personalizar la estructura de la FPGA integrada para crear una lógica especial para la aplicación. La programabilidad aporta la flexibilidad para adaptar los diseños a los estándares de comunicaciones nuevos o cambiantes, los protocolos de red así como para ajustar sus prestaciones.

emplo de aplicación: el impulso de la próxima generación

emplo de aplicación: el impulso de la próxima generación

En un diseño de control de tipo convencional (figura 4a) se utilizaría un procesador de señal digital (DSP) para desempeñar las funciones de control central, un ASIC de red para el/los protocolo/s de red y una FPGA para una parte de la funcionalidad añadida (en este caso para la ampliación de E/S). En cambio, en una implementación basada en FPGA con SoC, estos tres elementos se integran en una solo chip (figura 4b). La implementación de la FPGA en SoC también aumenta la funcionalidad existente al permitir el soporte a múltiples motores, múltiples protocolos de red y para IP de seguridad, con el fin de asegurar que el controlador se detenga de forma segura y cumpla los estándares de seguridad emergentes de la industria.

Las mejoras en prestaciones y consumo son significativas con la solución monochip. En un sistema de control, la velocidad del lazo de control es el parámetro más crítico para las prestaciones. La FPGA con SoC multiplica por 20 la velocidad del lazo de control respecto a la solución multichip, pasando así de 100µs a 5µs. Esto se traduce en una notable mejora de la eficiencia en el consumo que puede representar un 90% del coste total de funcionamiento. En este ejemplo, se estima que la energía consumida por el SoC es un 37% más baja que para su homólogo con tres chips.

La solución de FPGA con SoC reduce el coste total del sistema gracias a la integración y también al elevar la capacidad funcional del sistema. Al combinar tres o más dispositivo en un chip, la lista de materiales del sistema puede verse reducida. En este caso, el espacio ocupado en la placa también se ve reducido en un 57% mediante la implementación en SoC. Además, puede obtenerse una mayor funcionalidad con un coste más bajo. El SoC en este ejemplo ofrece soporte a dos motores, mientras que para la opción multichip tan sólo es uno. El soporte combinado a dos motores en un chip da como resultado un ahorro de costes del 53% si se compara con la duplicación de la configuración de dispositivo multichip para cada motor. El tamaño del SoC con la FPGA también puede adaptarse fácilmente para ofrecer soporte incluso a más sistemas para el control de motores con accionamiento integrado, así como a múltiples protocolos.

Un punto crítico

Un punto crítico

Los equipos de diseño que emplean la tecnología de SoC con FPGA pueden capitalizar sus notables ventajas en cuanto a productividad y competitividad. Los elementos de IP de hardware proporcionan las mejores prestaciones, el menor consumo y la mayor densidad posible, mientras que la estructura de la FPGA integrada ofrece la capacidad de diferenciar, aumentar y/o personalizar rápidamente la funcionalidad durante la fase de diseño o en campo. La plataforma programable en campo, junto con un diseño altamente automatizado y con un buen soporte, así como con herramientas de desarrollo de software, permiten que el equipo de diseño desarrolle un SoC personalizado, utilizando para ello dispositivos existentes en el mercado y en un tiempo mucho menor que el exigido por los ASIC o los dispositivos multichip. El diseño resultante es flexible, escalable y reutilizable, posibilitando así que el equipo se adapte y responda con rapidez a los nuevos mercados, cambios en los estándares y nodos de proceso más rápidos, así como para mantener productos con una larga vida operativa.

Con la aparición del SoC basado en FPGA se ha alcanzado un punto crítico como solución viable y ventajosa frente a las opciones convencionales de diseño para las aplicaciones actuales de sistemas embebidos. Con esta potente capacidad, los diseñadores no sólo superan las presiones que representan los retos de ejecución más presionantes, sino que también aportan ventajas en cuanto a plazo de comercialización, precio/prestaciones, diferenciación y longevidad del producto.

Autor:

Todd Koelling, responsable de productos embebidos en Altera

Suscripción papel: 180,00.- € (IVA inc.)

Suscripción PDF: 60,00.- € (IVA inc)

La automatización industrial se encuentra en una era de transformación, debido al aumento de la eficiencia operativa que posibilita la IA, la...

Los codificadores y sensores de posición rotativos disponibles actualmente en el mercado proporcionan un rango de medición absoluta de una sola...

Melexis presenta el MLX91235, un nuevo sensor de corriente que elimina la necesidad de un núcleo ferromagnético. El MLX91235 amplía la cartera de...

Toshiba Electronics Europe GmbH («Toshiba») presenta una nueva serie de CIs controlador de puerta para motores trifásicos de CC sin escobillas...

Suscríbete a nuestro boletín de noticias