Tel.: +34 91 706 56 69

Poema Sinfónico, 27. Esc B. Planta 1 Pta 5

28054 (Madrid - SPAIN)

e-mail: gm2@gm2publicacionestecnicas.com ó consultas@convertronic.net

El Internet de las cosas y la llegada de la informática ubicua han puesto de relieve la importancia de reducir el consumo de energía en toda la electrónica.

Si el futuro inmediato, verdaderamente, verá la conexión en red de todos los aparatos electrónicos y dispositivos hasta ahora no conectados, entonces el verdadero premio no es maximizar el rendimiento de la tecnología, (el rendimiento ya es lo suficientemente rápido para mantener IoT) es reducir lo suficiente el consumo de energía de los dispositivos electrónicos para que pueden funcionar de manera significativa dentro de esta nueva Internet.

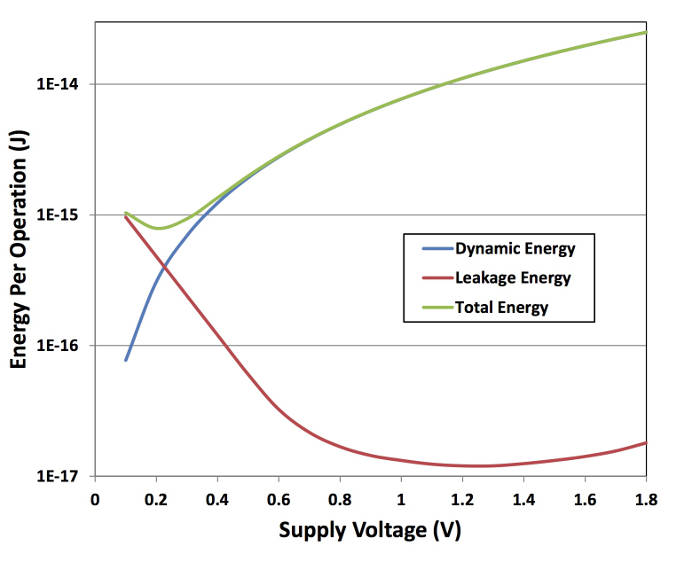

La energía se consume en dos formas fundamentales: como pérdida, cuando el estado de un circuito no está cambiando, y dinámicamente a medida que los nodos internos se cargan y descargan. Para circuitos reales en funcionamiento, la energía dinámica domina - especialmente para las tensiones de alimentación más altas, usadas en la mayoría de los diseños actuales (ver Figura 1).

La energía se consume en dos formas fundamentales: como pérdida, cuando el estado de un circuito no está cambiando, y dinámicamente a medida que los nodos internos se cargan y descargan. Para circuitos reales en funcionamiento, la energía dinámica domina - especialmente para las tensiones de alimentación más altas, usadas en la mayoría de los diseños actuales (ver Figura 1).

La energía dinámica se determina por la tensión de funcionamiento

Las técnicas subumbral son una manera de crear circuitos que consumen drásticamente menos energía que los construidos utilizando prácticas de diseño estándar. El diseño subumbral es un desafío, pero, dada la experiencia adecuada y diligencia, se puede hacer y con grandes beneficios.

Los resultados son circuitos que proporcionan las mismas funciones que los más tradicionales, pero utilizan una fracción de la energía. No hay compromiso en el rendimiento, robustez y fiabilidad. Estos chips pueden funcionar junto a sus homólogos tradicionales, sin ninguna diferencia visible desde el exterior - a excepción de la cantidad de energía necesaria para manejarlos. Pueden proporcionar importantes ahorros de energía para los diseñadores que construyen sistemas de eficiencia energética.

Debido a la naturaleza fundamental de estas innovaciones, las técnicas de diseño subumbral se pueden aplicar a prácticamente cualquier tipo de dispositivo CI.

El diseño subumbral se probó hace décadas

El diseño subumbral no es un concepto nuevo. Ya en la década de 1970, los relojeros suizos se dieron cuenta del potencial de hacer funcionar a algunos transistores en la región subumbral. La idea fue adoptada en los marcapasos y etiquetas RFID, pero nunca tuvo mucha aceptación más allá.

Lo que ha cambiado desde los años 70, cuando se crearon los primeros dispositivos subumbral comerciales, es la escala de aplicación. Los diseños del pasado utilizaron algunos transistores críticos subumbral - del orden de 10. En ese nivel, cada transistor se puede optimizar con la mano.

Ambiq crea chips completos que utilizan principalmente transistores subumbral. Esto equivale a millones de transistores y no se puede hacer a mano, pero se basa en herramientas de diseño estándar y se utiliza para crear chips de superumbral. Estos son los que Ambiq ha logrado con el fin de comercializar los circuitos subumbral.

El enfoque de Ambiq Micro se mueve más allá de las mejoras incrementales que otras empresas de semiconductores han tomado y produce avances revolucionarios a través de un enfoque único para el problema: diseño de circuito subumbral. Estas consideraciones condujeron el desarrollo y la comercialización de la tecnología subumbral patentada Power Optimized Technology (SPOT™) de Ambiq, que Ambiq utiliza para construir, circuitos fiables y robustos que consumen drásticamente menos energía en un proceso rentable de fabricación.

Consumo de energía en electrónica

Debido a que la energía dinámica varía de forma exponencial con la tensión de funcionamiento, la tensión se convierte en la palanca más grande para reducir el consumo de energía dinámica (mientras que también tiene un impacto tangible, pero menos dramáticp, en las pérdidas). Por ejemplo, cuando se compara con un circuito típico que funciona a 1,8 V, un circuito de "cerca de umbral" que funciona a 0,5V puede lograr una mejora de hasta 13X en la energía dinámica. Un circuito aún más agresivo "subumbral" que funciona a 0,3V, ¡puede lograr una mejora de hasta 36X!-

Los diseños digitales tradicionales utilizan el estado del transistor - "on" u "off" - como un concepto fundamental para la implementación de la lógica. Los diseños analógicos, de forma paralela, asumen que un transistor está "on" hasta cierto punto controlado, uso para amplificar. Pero el funcionamiento subumbral significa que ninguna de las tensiones en los chips está por encima del umbral de voltaje (Vth), así que los transistores nunca se encienden. Incluso una lógica tensión "alta" mantiene los transistores "off". Esto significa que se requieren enfoques completamente nuevos de diseño.

Los retos del subumbral moderno

Los retos del subumbral moderno

La adaptación de los flujos de superumbral estándar y la infraestructura para el diseño subumbral presenta numerosos retos, empezando por los propios transistores:

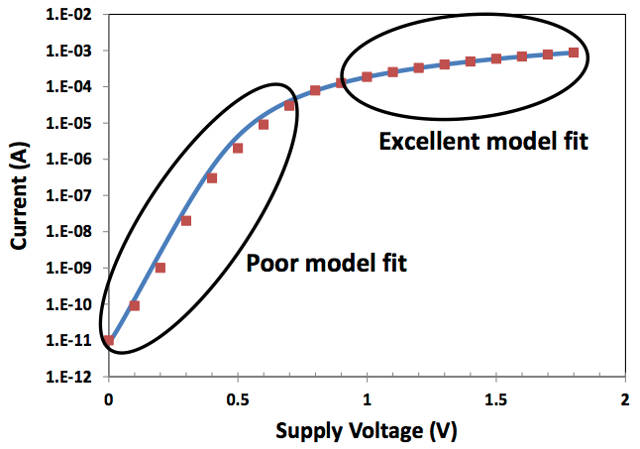

1. Modelos de transistores pobres

El modelo de transistor constituye la base de todo en un diseño de circuito integrado. Todas las simulaciones, todas las abstracciones y la automatización, el propio proceso de cierre de diseño: todos se basan en un modelo de transistor exacto. La mayoría de modelos de transistores se han centrado en las características "on" del dispositivo, poniendo poca atención en el "off". Toda la región entre 0 V y Vth, normalmente no consigue modelar con la misma precisión, y los modelos existentes no son adecuados para el diseño subumbral, como se muestra en la Figura 2.

2. Los cambios de la lógica y el ruido

2. Los cambios de la lógica y el ruido

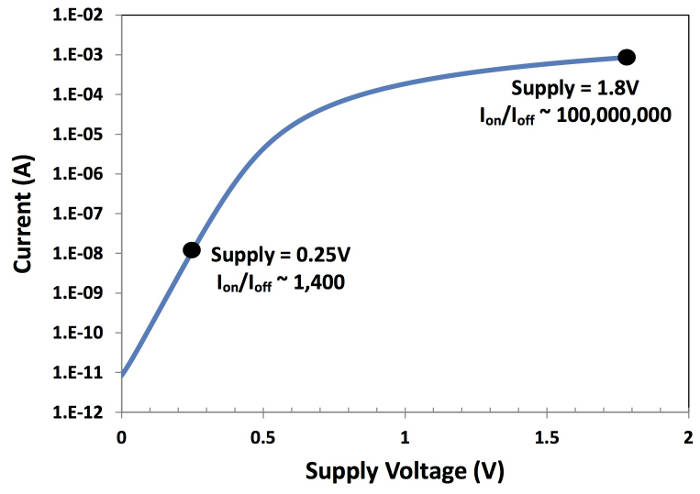

La respuesta de salida de un transistor en el régimen subumbral es sutil; detectarla requiere una gran sensibilidad. Las corrientes cambian de manera exponencial en respuesta a los cambios de tensión, pero son corrientes sumamente pequeñas. Además, la proporción de corriente "on" a "off" es del orden de 1000, órdenes de magnitud menos de la experiencia de diseño superumbral (ver Figura 3). Como es de esperar, el ruido externo puede interferir mucho más fácilmente con un funcionamiento limpio.

3. Sensibilidad a las condiciones de funcionamiento

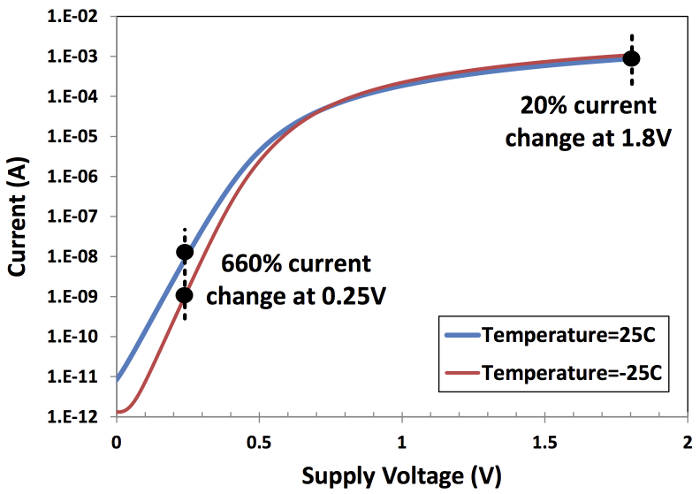

Los diseños subumbral también son mucho más susceptibles a los cambios en el proceso y la variación ambiental que los diseños superumbral. Por ejemplo, la corriente en una curva lenta proceso puede ser 10-100 veces menor que la de un proceso nominal. Teniendo en cuenta que la proporción de corriente encendido / apagado (arriba), es sólo del orden de mil, esto no puede ser ignorado. Las variaciones de temperatura son un buen ejemplo de cómo las condiciones ambientales crean un desafío para el diseñador. Vth depende de la temperatura, y el Ion depende exponencialmente de V (como se muestra en la Figura 4 a continuación). Como resultado, la corriente "off" a temperatura elevada es similar en valor a la corriente "on" a temperatura reducida para un circuito no compensado. Por lo tanto, el diseño de circuitos subumbral requiere un esfuerzo adicional para asegurarse de que los circuitos funcionarán como se espera en todas las condiciones de funcionamiento especificadas.

Las variaciones de temperatura son un buen ejemplo de cómo las condiciones ambientales crean un desafío para el diseñador. Vth depende de la temperatura, y el Ion depende exponencialmente de V (como se muestra en la Figura 4 a continuación). Como resultado, la corriente "off" a temperatura elevada es similar en valor a la corriente "on" a temperatura reducida para un circuito no compensado. Por lo tanto, el diseño de circuitos subumbral requiere un esfuerzo adicional para asegurarse de que los circuitos funcionarán como se espera en todas las condiciones de funcionamiento especificadas.

4. Los retos logísticos

Gran parte del flujo de fabricación se basa en suposiciones razonables para diseños superumbral, si bien se descomponen para diseños subumbral. Uno de los retos obvios se puede encontrar en los probadores utilizados para validar el silicio durante la producción. Las unidades de medida paramétricas (PMUs) que prueban las tensiones y corrientes, están diseñados para medir microamperios, no nano o picoamperios.

Incluso algo tan sencillo como la caracterización del dispositivo tiene que ser repensado simplemente debido a las sensibilidades que tienen los circuitos subumbral, y que los circuitos superumbral no tienen. Los flujos de caracterización típicos pueden no ser lo suficientemente minuciosos, para demostrar que los circuitos funcionan correctamente en todas las condiciones imaginables.

La naturaleza fundamental de estos desafíos, combinada con el hecho de que pocos ingenieros son expertos en el tratamiento de problemas subumbral, explica el reto de la comercialización de circuitos subumbral.

Las soluciones de Ambiq

La tecnología SPOT de Ambiq se dirige a superar todos estos retos. Además, las técnicas de diseño subumbral se pueden aplicar a prácticamente cualquier tipo de dispositivo CI. Por ejemplo, Ambiq demostró la viabilidad de este enfoque innovador con la introducción del RTC (Real Time Clock) de menor potencia del mundo en 2013. La próxima versión de microcontrolador de 32 bits (MCU) basado en ARM de menor potencia del mundo, que demuestra aún más la viabilidad de extender estas técnicas a una plataforma completamente diferente. Ambiq Micro está comprometida a ampliar la Plataforma SPOT - y dar a las baterías una vida mejor.

Suscripción papel: 180,00.- € (IVA inc.)

Suscripción PDF: 60,00.- € (IVA inc)

Power Integrations ha presentado un nuevo miembro de su familia InnoMux™-2 de circuitos integrados de fuente de alimentación offline de una sola...

Melexis presenta el MLX92235, un conmutador de efecto Hall de potencia ultrabaja con las mejores tolerancias de su clase para una frecuencia de...

Mecter se complace en anunciar el lanzamiento de los nuevos circuitos integrados periféricos de teclas táctiles de Holtek, la serie BS21xC-x. Estos...

La rápida transición hacia medios de transporte climáticamente neutros y energéticamente eficientes supone una contribución importante a un futuro...

Suscríbete a nuestro boletín de noticias