Tel.: +34 91 706 56 69

Poema Sinfónico, 27. Esc B. Planta 1 Pta 5

28054 (Madrid - SPAIN)

e-mail: gm2@gm2publicacionestecnicas.com ó consultas@convertronic.net

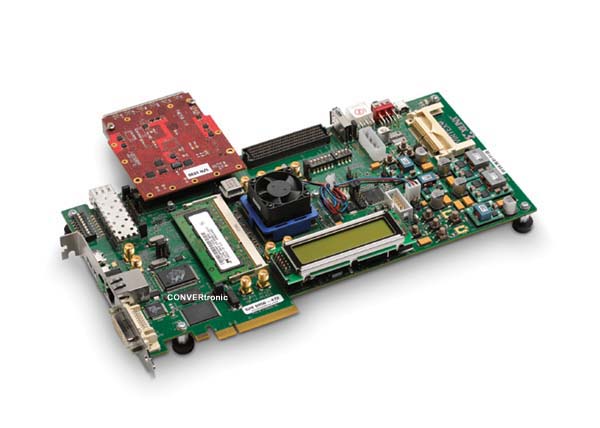

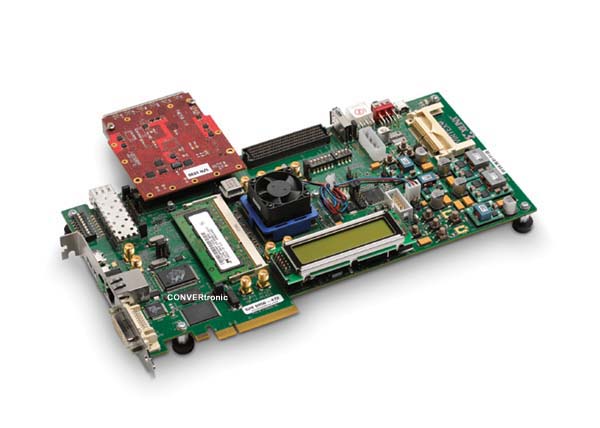

MathWorks tiene disponible EDA Simulator Link 3.3 con nuevas funciones FPGA-in-the-loop (FIL) para placas de desarrollo de FPGA de Xilinx. FIL permite a los ingenieros verificar sus diseños a velocidades de hardware mientras utilizan Simulink como test bench a nivel de sistema.

MathWorks tiene disponible EDA Simulator Link 3.3 con nuevas funciones FPGA-in-the-loop (FIL) para placas de desarrollo de FPGA de Xilinx. FIL permite a los ingenieros verificar sus diseños a velocidades de hardware mientras utilizan Simulink como test bench a nivel de sistema.

La introducción de FIL se añade al exhaustivo conjunto de opciones de verificación HDL que EDA Simulator Link permite para algoritmos creados en MATLAB y Simulink. La verificación basada en FPGA proporciona un rendimiento en tiempo de ejecución significativamente mayor del que es posible con simuladores HDL y aumenta la confianza en que el algoritmo funcione en el mundo real.

Entre las características principales del producto se incluyen las capacidades de:

- Verificar implementaciones HDL de código MATLAB y modelos Simulink mediante placas de desarrollo FPGA para dispositivos de clase Spartan y Virtex, incluida la placa de desarrollo Virtex-6 ML605.

- Verificar implementaciones HDL de código MATLAB y modelos Simulink empleando cosimulación con Mentor Graphics ModelSim, Mentor Graphics Questa y Cadence Design Systems Incisive Enterprise Simulator.

- Generar componentes TLM 2.0 para su uso en entornos de prototipado virtual en SystemC.

Suscripción papel: 180,00.- € (IVA inc.)

Suscripción PDF: 60,00.- € (IVA inc)

Suscríbete a nuestro boletín de noticias