Tel.: +34 91 706 56 69

Poema Sinfónico, 27. Esc B. Planta 1 Pta 5

28054 (Madrid - SPAIN)

e-mail: gm2@gm2publicacionestecnicas.com ó consultas@convertronic.net

Este artículo presenta un kit de evaluación compacto para demostrar el alto rendimiento de los MOSFETs de SiC de 4.ª generación de ROHM con una vanguardista corrección del factor de potencia (PFC) de totem pole. Además de mostrar métricas de rendimiento claves, tales como mediciones de eficiencia, el artículo describe algunos retos de diseño de la topología disponible y cómo han sido abordados con el fin de obtener una PFC con entrada universal.

La topología de PFC de polo tótem (TP-PFC) como tal ha sido analizada en el pasado en múltiples artículos, p. ej. en esta revista en [1]. Con la disponibilidad de los semiconductores WBG que incorporan diodos de cuerpo de alto rendimiento, dicha topología se está volviendo muy atractiva. Su ventaja clave con respecto a la tradicional PFC de tipo boost reside en eliminar la rectificación de baja frecuencia y la pérdida de potencia asociada a la caída de tensión en sentido directo de un rectificador de 50 Hz. Por lo tanto se pueden alcanzar eficiencias por encima del 98 % y, si se utiliza una etapa secundaria adecuada con una eficiencia similar, se puede alcanzar la eficiencia perseguida de 80+ Titanium.

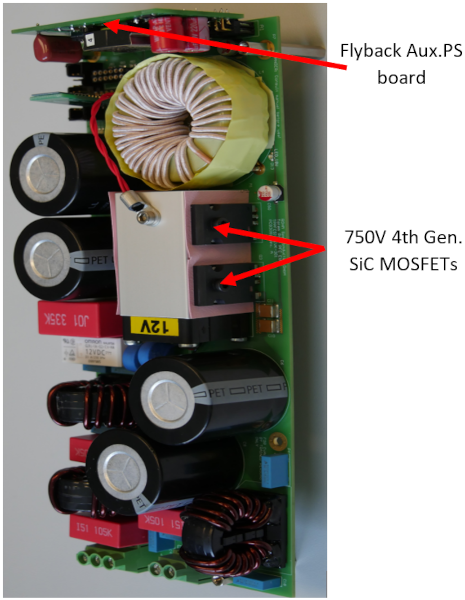

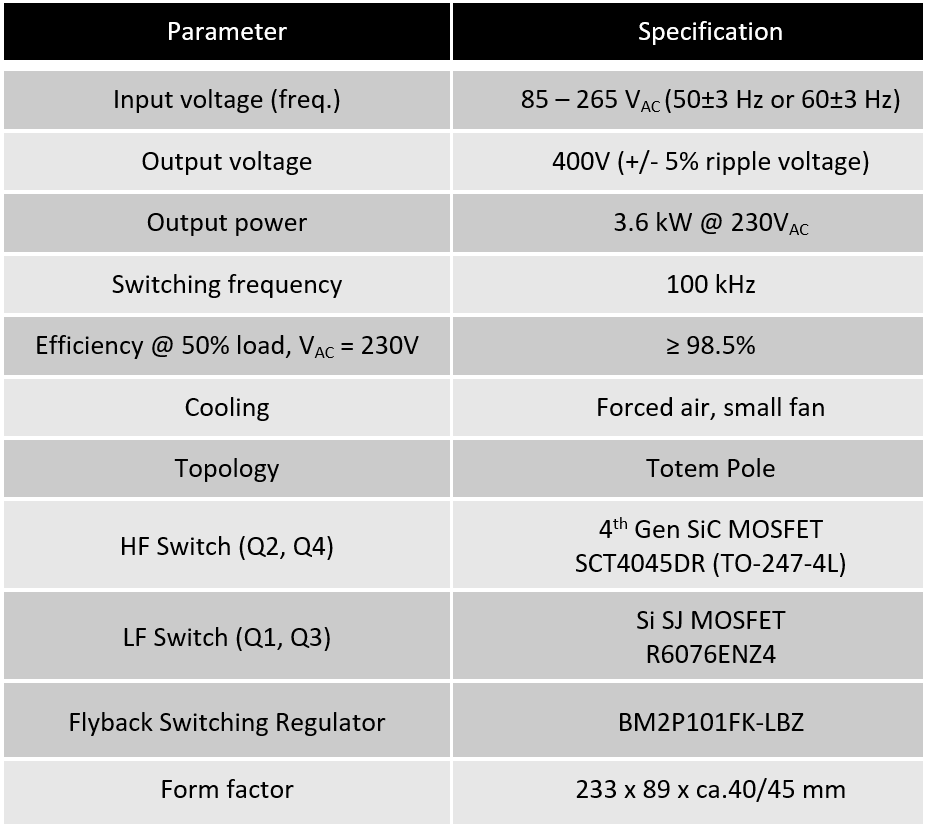

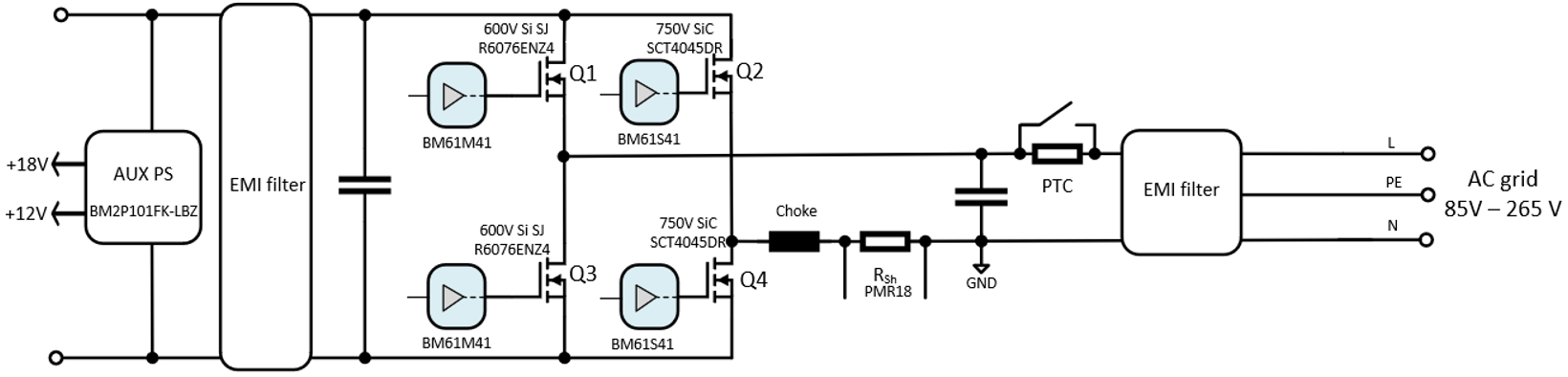

En la Figura 1 se muestra, junto con algunas de las especificaciones de diseño, una imagen del kit de evaluación (EVK) expuesto que implementa la TP-PFC con corriente nominal de entrada de 16 A. Los dispositivos clave utilizados en esta placa aparecen destacados en la figura 1. Además de los MOSFETs de SiC de 4.ª generación, este diseño emplea MOSFETs de Si SJ de ROHM, así como los controladores de puerta BM61S41/BM61M41 y otros componentes de ROHM, tales como la resistencia de derivación y el circuito integrado (IC) de regulador de conmutación flyback en la alimentación eléctrica auxiliar.

Figura 2: Diagrama de circuito de TP-PFC

El rendimiento del EVK desarrollado aparece ilustrado en los siguientes gráficos mostrando la eficiencia medida y el factor de potencia de entrada alcanzado en la entrada CA tanto de 230 V como de 115 V.

Con respecto a la eficiencia, cabe señalar que incluye todo el consumo de energía de a bordo correspondiente a las fuentes de alimentación auxiliares para los controladores de compuerta, la electrónica de baja tensión y el ventilador. Puede verse que se alcanza el requisito de un factor de potencia > 0,95 con una carga del 20 %. Si el circuito PFC se combina con una etapa CC/CC de eficiencia adecuadamente elevada, el diseño también puede cumplir los requisitos de eficiencia de 80+ Titanium.

Con respecto a la eficiencia, cabe señalar que incluye todo el consumo de energía de a bordo correspondiente a las fuentes de alimentación auxiliares para los controladores de compuerta, la electrónica de baja tensión y el ventilador. Puede verse que se alcanza el requisito de un factor de potencia > 0,95 con una carga del 20 %. Si el circuito PFC se combina con una etapa CC/CC de eficiencia adecuadamente elevada, el diseño también puede cumplir los requisitos de eficiencia de 80+ Titanium.

a) Eficiencia medida b) Factor de potencia medido

Figura 3- Eficiencia y factor de potencia medidos

Los siguientes párrafos analizan cómo ha sido desarrollado este diseño y cómo han sido abordados ciertos aspectos desafiantes de esta topología. Entre tales desafíos figuran:

• Encontrar los ajustes correctos para tiempo muerto y supresión.

• Arranque automático seguro en la tensión de entrada universal de la red eléctrica.

• Arranque suave en torno al cruce por cero CA para minimizar picos de corriente.

Antes se destacarán las ventajas de los MOSFETs de SiC de 4.ª generación de ROHM.

MOSFET de SiC de 4.ª generación de ROHM

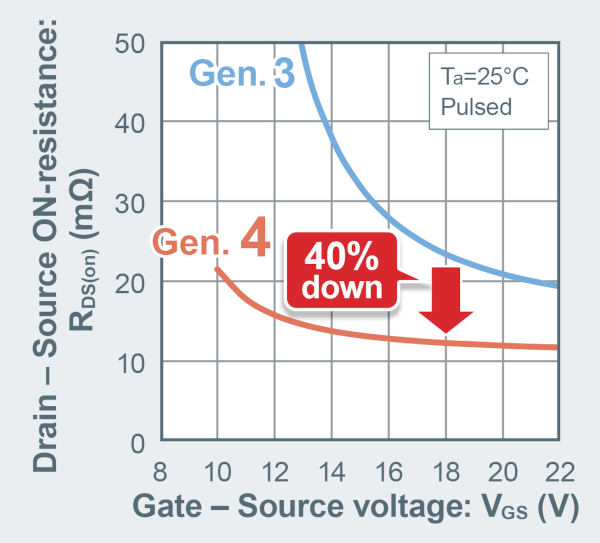

Los nuevos MOSFETs de SiC consiguen una importante reducción del 40 % en la resistencia de estado activado por unidad de área en comparación con los MOSFETs de SiC de 3.ª generación. Esta reducción se consigue sin sacrificar la robustez de cortocircuito: confiriendo a los nuevos dispositivos solidez y alto rendimiento en grado sumo.

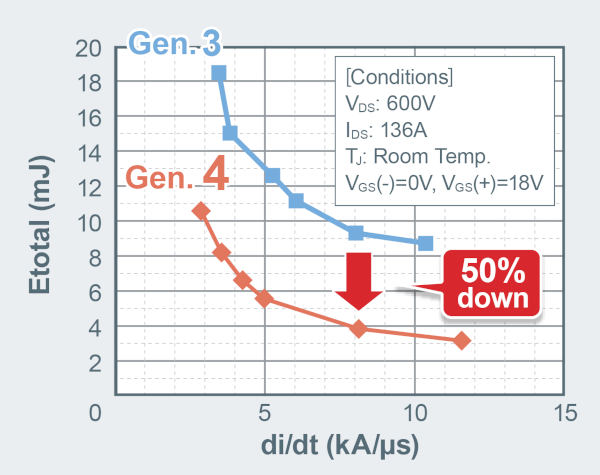

Además, las pérdidas de conmutación en los MOSFETs de SiC de 4.ª generación son un 50 % menores que en la 3.ª generación gracias a una capacitancia parásita de puerta-drenaje “CGD” drásticamente reducida. Esto se traduce en una mayor eficiencia de conversión.

a) Reducción de la resistencia de estado activado en los MOSFETs de SiC de 4.ª generación. b) Comparación de pérdida de conmutación entre los MOSFETs de SiC de 3.ª y los de 4.ª generación.

Figura 4: Reducción de pérdida de conmutación y resistencia de estado activado en los MOSFETs de SiC de 4.ª generación de ROHM

Figura 4: Reducción de pérdida de conmutación y resistencia de estado activado en los MOSFETs de SiC de 4.ª generación de ROHM

Para dirigir la puerta, en contraste con la tensión de puerta-drenaje “VGS” de 18 V requerida en los MOSFETs de SiC de 3.ª generación y anteriores, los nuevos productos admiten un rango de tensión de puerta más flexible (15-18 V). Además, debido a la reducción de la capacitancia parásita “CGD” y, por lo tanto, la relación entre CGS y CGD, los MOSFETs de SiC de 4.ª generación pueden ser desconectados de forma segura con tan solo 0 V sin conexión parásita que pueda ser causada por una elevada dVDS/dt. Como resultado, el circuito controlador de puerta puede simplificarse eliminando la necesidad de una polarización negativa para la desconexión.

Para dirigir la puerta, en contraste con la tensión de puerta-drenaje “VGS” de 18 V requerida en los MOSFETs de SiC de 3.ª generación y anteriores, los nuevos productos admiten un rango de tensión de puerta más flexible (15-18 V). Además, debido a la reducción de la capacitancia parásita “CGD” y, por lo tanto, la relación entre CGS y CGD, los MOSFETs de SiC de 4.ª generación pueden ser desconectados de forma segura con tan solo 0 V sin conexión parásita que pueda ser causada por una elevada dVDS/dt. Como resultado, el circuito controlador de puerta puede simplificarse eliminando la necesidad de una polarización negativa para la desconexión.

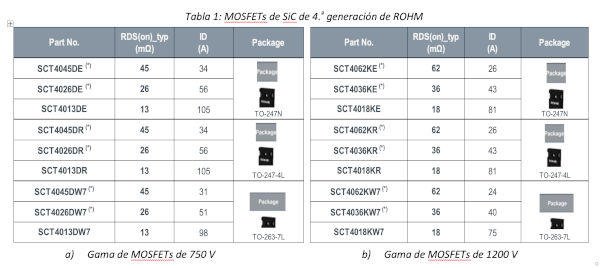

La tabla 1 muestra la gama de MOSFETS de SiC de 4.ª generación de 750 V y 1200 V de ROHM. Los dispositivos se hallan disponibles en versión THD (dispositivo de agujero pasante) TO-247N y TO-247-4L, así como en versión SMD (dispositivo de montaje superficial) TO-263-7L. La cualificación de automoción está prevista para todos los dispositivos marcados con un asterisco (*).

La tabla 1 muestra la gama de MOSFETS de SiC de 4.ª generación de 750 V y 1200 V de ROHM. Los dispositivos se hallan disponibles en versión THD (dispositivo de agujero pasante) TO-247N y TO-247-4L, así como en versión SMD (dispositivo de montaje superficial) TO-263-7L. La cualificación de automoción está prevista para todos los dispositivos marcados con un asterisco (*).

a) Gama de MOSFETs de 750 V b) Gama de MOSFETs de 1200 V

Tabla 1: MOSFETs de SiC de 4.ª generación de ROHM

Configuración de tiempo muerto y supresión

Los errores asociados a la detección del cruce por cero CA, así como los elementos parásitos de los MOSFETs deben ser tenidos en cuenta al configurar el control PWM (modulación por ancho de pulso). En este EVK de TP-PFC se ha insertado un tiempo de supresión de 50 µs en torno al cruce por cero CA. Durante el cual, los cuatro conmutadores son desconectados poco antes del cruce por cero, ya sea de positivo a negativo o de negativo a positivo, para evitar el disparo (shoot-through). El bucle de control queda paralizado durante este tiempo para evitar que la acumulación del integrador provoque un pico de alta corriente no deseado mediante la aplicación de un impulso PWM amplio en la siguiente conexión. Un breve tiempo de supresión posibilita una mayor controlabilidad sobre la forma de onda de la corriente, un menor coeficiente THD (distorsión armónica total) y una eficiencia relativamente superior. No obstante, el tiempo de supresión mínimo queda limitado por la velocidad de muestreo del controlador y la frecuencia de línea.

Además del tiempo de supresión en torno al cruce por cero CA, un tiempo muerto apropiado debe ser ajustado entre los comandos de control de los MOSFETs de SiC complementarios. A partir de la hoja de datos del controlador de puerta BM61S41, el retardo de propagación tiene un valor máximo de 65 ns. Sumando otros 10 ns máx. para los resultados de la desadaptación de propagación PWM se traduce en un tiempo muerto mínimo absoluto de 75 ns. Para tener en cuenta los retardos de conexión y desconexión de los MOSFETs de SiC y para tener algo de margen, el tiempo muerto para esta placa ha sido ajustado en 150 ns. Como es natural, esto necesita ser evaluado para cada diseño y también se ve afectado por la selección de resistencias de puerta de conexión y de desconexión.

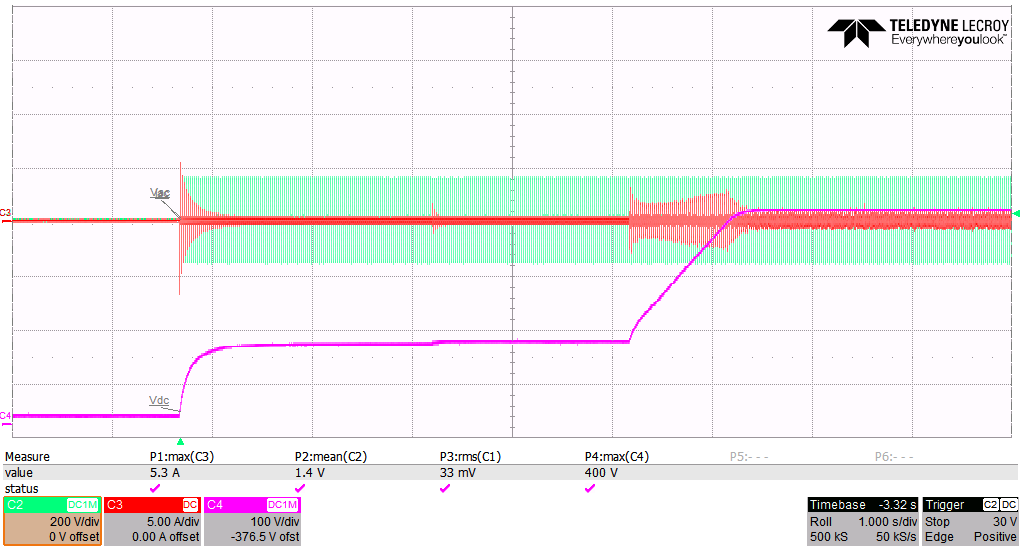

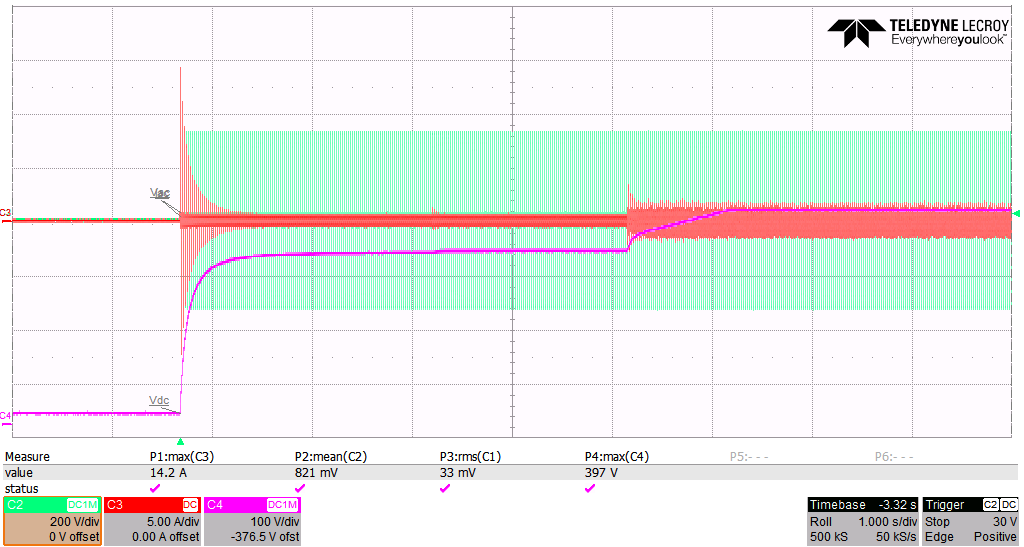

Arranque automático en una entrada de red eléctrica universal

El EVK de TP-PFC viene equipado con un PTC para precarga en paralelo con un relé de derivación. Al arrancar, el relé es desconectado y los condensadores masivos son precargados a través del PTC hasta un umbral seguro antes de conectar el relé y operar el convertidor. Esto evita que el circuito se dañe debido a elevadas corrientes de irrupción. El EVK ha sido probado para todo el rango de entrada universal [85 Vca-265 Vca], habiéndose demostrado que es seguro para un arranque automático incluso a 265 Vca. Gracias al Bucle Cerrado en Frecuencia - Integrador Generalizado de Segundo Orden (SOGI-FLL) implementado, este EVK también puede rastrear y detectar desviaciones en la frecuencia de la red eléctrica de 50±3 Hz o 60±3 Hz.

a) Arranque automático 110 Vca, 400 Vcc b) Arranque automático 230 Vca, 400 Vcc Figura 5: Arranque automático PFC vs. tensión de entrada CA

Figura 5: Arranque automático PFC vs. tensión de entrada CA

Medidas para minimizar picos de corriente tras el cruce por cero CA

En la topología TP-PFC, la secuencia de conmutación de MOSFET es de importancia crucial. No entender ni observar los retos de control en una TP-PFC puede dar lugar a un funcionamiento inadecuado, problemas de EMI inesperados o incluso fallo de los dispositivos de potencia. El reto más común que es inherente a esta topología es la aparición de picos de corriente en el cruce por cero CA [2],[3]. Estos son originados principalmente por el condensador parásito de salida “COSS” y la carga de recuperación inversa asociada “Qrr” de los MOSFETs conmutados de frecuencia de línea, que solo cambian estado en el cruce por cero CA.

En [2] se presenta un análisis detallado de los picos de corriente CA y formas de onda en una topología TP-PFC.

En [2] se presenta un análisis detallado de los picos de corriente CA y formas de onda en una topología TP-PFC.

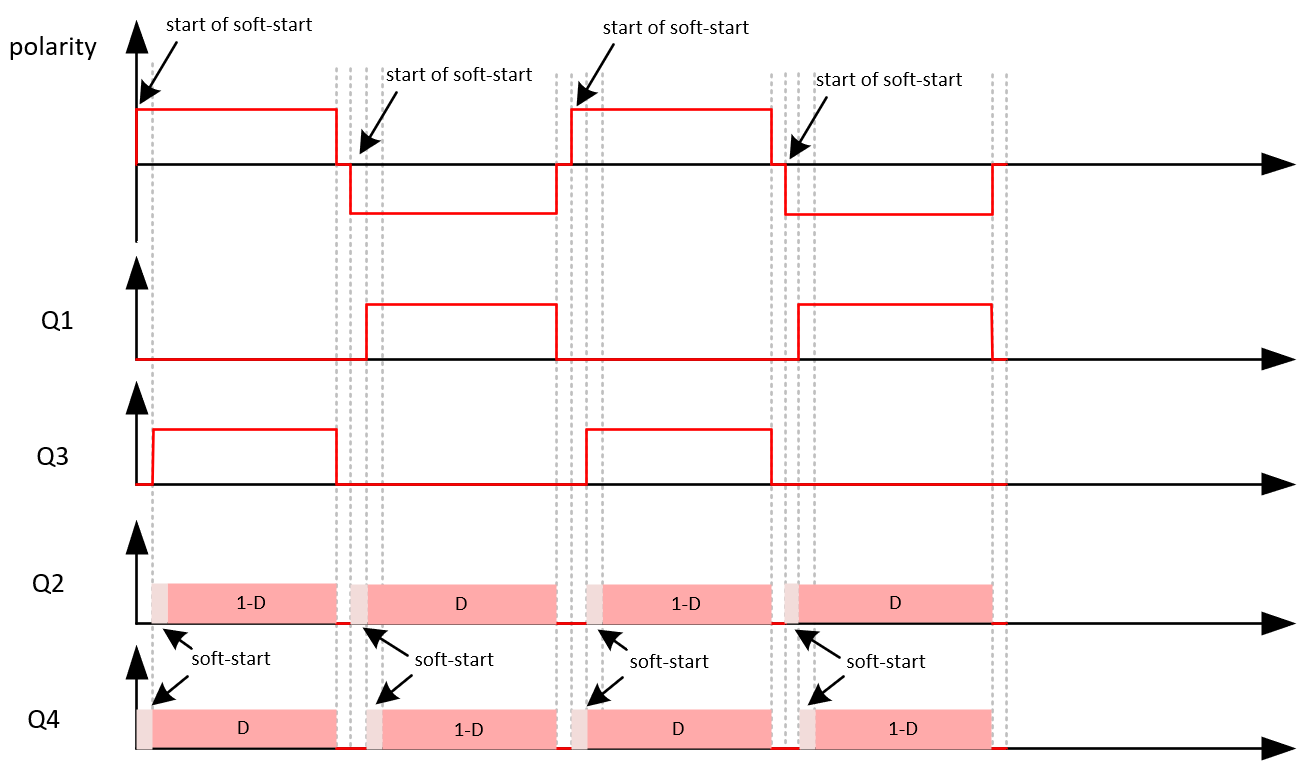

En el EVK de TP-PFC de ROHM, una secuencia de arranque suave es implementada después de cada cruce por cero CA. Esto implica un aumento de los ciclos de servicio aplicados a los MOSFETs de SiC de alta frecuencia (Q2, Q4), así como control preciso sobre la conexión de los MOSFETs de Si SJ de baja frecuencia. La implementación de este arranque suave alcanzó picos de corriente significativamente menores. La secuencia de conmutación de MOSFET implementada se muestra en la fig. 6.

Figura 6: Arranque suave de MOSFETs en TP-PFC

Figura 6: Arranque suave de MOSFETs en TP-PFC

Los MOSFETs Q2 y Q4 son conmutados complementariamente. Durante el medio ciclo negativo, el MOSFET Q2 es el conmutador activo que es controlado por el ciclo de servicio calculado “D”. Durante este tiempo, el MOSFET Q4 está funcionando en modo de rectificación síncrona en ciclo de servicio “1-D”. Obsérvese que el MOSFET Q1 solo se conmuta a la frecuencia de la red eléctrica y permanece encendido durante el medio ciclo negativo completo para proporcionar una vía de retorno de baja impedancia hacia la red eléctrica. El funcionamiento se vuelve a invertir durante el medio ciclo positivo y los MOSFETs de lado alto y de lado bajo de cada rama intercambian su función.

Conforme la tensión de entrada cambia la polaridad del medio ciclo negativo al positivo, y justo después del cruce por cero CA, se activa la secuencia de arranque suave del MOSFET Q4. Esta secuencia consiste en aplicar un factor de incremento a la anchura de impulso de forma que aumente gradualmente el tiempo de encendido de este MOSFET desde el 0 % al 100 % del ciclo “D” calculado. Mientras esto tiene lugar, el MOSFET Q1 procede a la recuperación inversa completa y la “VDS” de Q3 se reduce a tierra. Así pues, el pico positivo de corriente, originado por la lenta recuperación de Q1 y la elevada tensión “VDS” en el MOSFET Q3, es eliminado.

Sabiendo que la tensión CA es muy baja justo después del cruce por cero y dado que el inductor ya se halla cargado con la tensión del bus CC, una gran corriente inversa negativa fluirá por el inductor de vuelta a la red principal. Esto da lugar a un elevado pico negativo de corriente al conectar el MOSFET síncrono Q2 incluso en ciclo de servicio “1-D”. Por lo tanto, una vez que Q4 alcanza el ciclo “D” completo, el arranque suave también se aplica al MOSFET síncrono Q2 para reducir este pico negativo casi a cero. Simultáneamente, al arrancar Q2 suavemente, Q3 debe ser conectado para proporcionar la vía de retorno a la red eléctrica.

Un elevado pico negativo de corriente también aparecerá en el cruce por cero CA si el MOSFET Q3 se enciende demasiado tarde tras completarse el arranque suave de Q2 según se detalla en [2].

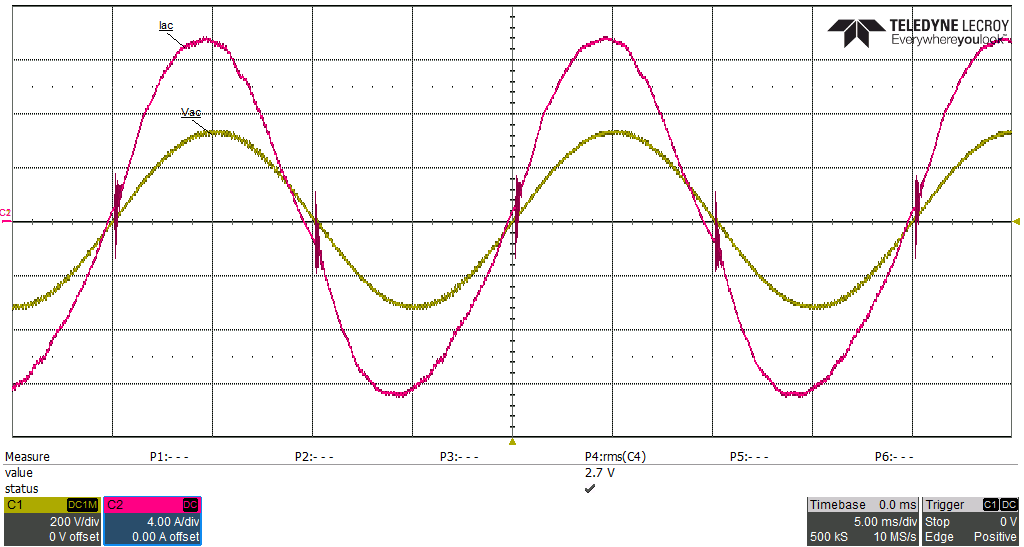

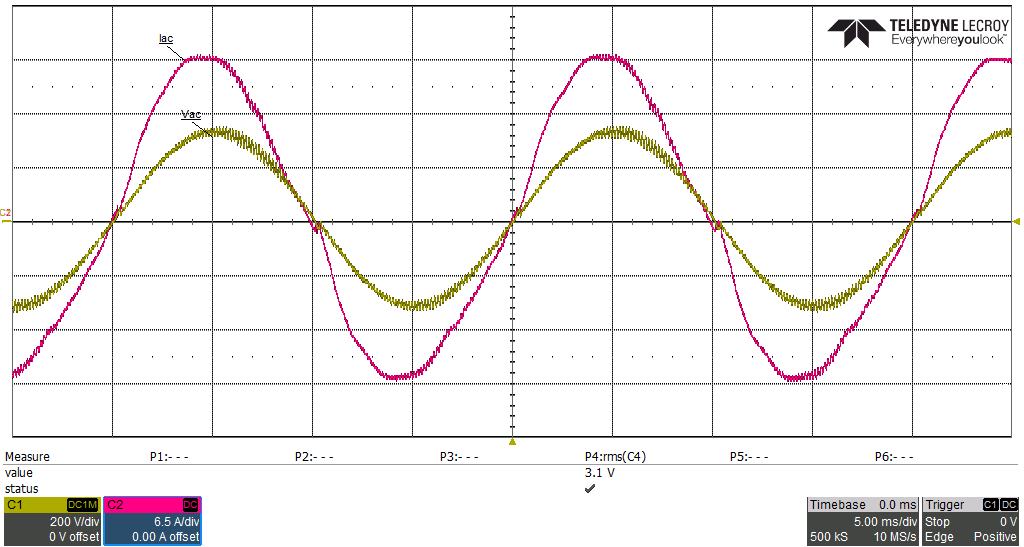

Resultados experimentales La figura 7 muestra la forma de onda de la corriente de entrada en torno al cruce por cero CA con y sin el arranque suave.

La figura 7 muestra la forma de onda de la corriente de entrada en torno al cruce por cero CA con y sin el arranque suave.

a) Control tradicional sin arranque suave b) Con método de arranque suave

Figura 7: Picos de corriente de entrada en el cruce por cero CA con y sin método de arranque suave

(rojo: ICA, verde: VCA)

Obsérvese que, dado que ''1-D'’ es muy bajo cuando Q2 se conecta por primera vez, se hace incluso menor y tiende a cero al multiplicarse por los factores de arranque suave. En función del controlador de puerta utilizado, Q2 puede permanecer desactivado durante un par de ciclos PWM hasta que el término ''1-D'' pase a ser mayor que el tiempo de activación PWM mínimo del controlador de puerta. Esto se traduce en un pico de corriente residual pero muy bajo, positivo y negativo, en cada cruce por cero CA. La secuencia de control de MOSFETs explicada en la sección anterior fue implementada y probada en el EVK de TP-PFC de 3,6 kW. A partir de los resultados de las pruebas, sin este método de control, los picos de corriente tanto positivos como negativos están presentes. La aplicación del arranque suave a MOSFETs tanto activos como síncronos, así como la conexión de los MOSFETs de baja frecuencia en el momento preciso, ha arrojado mejores formas de onda de corriente y ha ayudado a lograr un coeficiente THD mucho menor.

La secuencia de control de MOSFETs explicada en la sección anterior fue implementada y probada en el EVK de TP-PFC de 3,6 kW. A partir de los resultados de las pruebas, sin este método de control, los picos de corriente tanto positivos como negativos están presentes. La aplicación del arranque suave a MOSFETs tanto activos como síncronos, así como la conexión de los MOSFETs de baja frecuencia en el momento preciso, ha arrojado mejores formas de onda de corriente y ha ayudado a lograr un coeficiente THD mucho menor.

Resumen

El EVK de TP-PFC presentado muestra un alto rendimiento en importantes aspectos de diseño, incluidas características de control y una elevada eficiencia, alcanzando el 98,5 % al tiempo que se incluye todo el consumo de energía de a bordo correspondiente a las fuentes de alimentación auxiliares y al ventilador. Tanto una baja resistencia de estado activado como una baja pérdida de conmutación de los MOSFETs de SiC de 4.ª generación han ayudado a alcanzar semejante rendimiento. Los resultados demuestran la idoneidad de estos nuevos productos para numerosas aplicaciones de conversión de energía tales como, por ejemplo, fuentes de alimentación de servidores y centros de datos, fuentes de alimentación para telecomunicaciones e industria (SMPS), sistemas de almacenamiento de energía, así como en el interior de vehículos eléctricos (p. ej. OBC) donde son necesarios una elevada densidad de potencia, eficiencia, circuitos de puerta sencillos y robustez de cortocircuito.

Referencias:

[1] Christian Felgemacher, Aly Mashaly “SiC Based Totem Pole PFC for Industrial Power Supplies”, Bodo’s Power Systems, febrero 2020.

[2] Bosheng Sun, Analog Application Journal “How to reduce current spikes at AC zero-crossing for totem-pole PFC” Bosheng Sun, https://www.ti.com/lit/an/slyt650

[3] L. Xue, Z. Shen, D. Boroyevich and P. Mattavelli, "GaN-based high frequency totem-pole bridgeless PFC design with digital implementation," 2015 IEEE Applied Power Electronics Conference and Exposition (APEC), 2015, pp. 759-766, doi: 10.1109/APEC.2015.7104435.

Suscripción papel: 180,00.- € (IVA inc.)

Suscripción PDF: 60,00.- € (IVA inc)

Suscríbete a nuestro boletín de noticias