Macro MRAM embebida con lectura aleatoria de más de 200 MHz y un rendimiento de escritura de 10,4 MB/s para MCUs de alto rendimiento

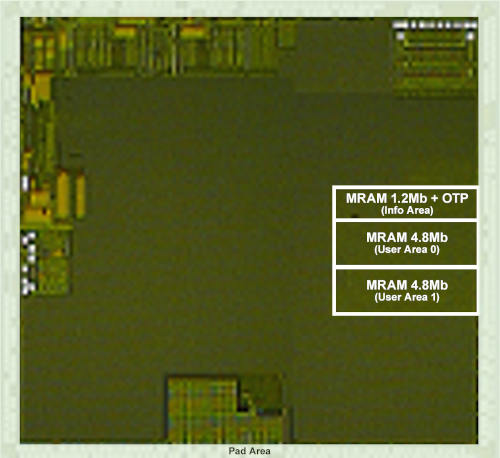

Renesas Electronics Corporation ha anunciado que ha desarrollado tecnologías de circuitos para un chip de prueba de memoria magnetorresistiva de acceso aleatorio (STT-MRAM, en adelante MRAM) con rápidas operaciones de lectura y escritura. Fabricado mediante un proceso de 22 nm, el chip de prueba de la unidad microcontroladora (MCU) incluye una matriz de celdas de memoria MRAM integrada de 10,8 megabits (Mbit). Alcanza una frecuencia de acceso de lectura aleatoria de más de 200 MHz y un rendimiento de escritura de 10,4 megabytes por segundo (MB/s).

A medida que avanzan las tecnologías IoT y AI, se espera que los MCU utilizados en dispositivos de punto final ofrezcan más rendimiento que nunca. Las frecuencias de reloj de la CPU de las MCU de alto rendimiento están en los cientos de MHz, por lo que para lograr un mayor rendimiento, es necesario aumentar las velocidades de lectura de la memoria no volátil integrada para minimizar la brecha entre ellas y las frecuencias de reloj de la CPU. La MRAM tiene un margen de lectura menor que la memoria flash utilizada en los MCU convencionales, lo que dificulta las operaciones de lectura a alta velocidad. Por otro lado, en cuanto al rendimiento de escritura, la MRAM es más rápida que la memoria flash porque no requiere ninguna operación de borrado antes de realizar las operaciones de escritura.

Por otro lado, en lo que respecta al rendimiento de escritura, la MRAM es más rápida que la memoria flash porque no requiere ninguna operación de borrado antes de realizar las operaciones de escritura. Sin embargo, acortar los tiempos de escritura es deseable no sólo para el uso cotidiano, sino también para reducir los costes de escritura de patrones de prueba en los procesos de prueba y de escritura de códigos de control por parte de los fabricantes de productos finales.

Para hacer frente a estos retos, Renesas ha desarrollado las siguientes nuevas tecnologías de circuitos para conseguir operaciones de lectura y escritura más rápidas en MRAM.

(1) Tecnología de lectura rápida

La lectura de MRAM se realiza generalmente mediante un amplificador diferencial (amplificador sensor) para determinar cuál de las dos corrientes, la de la célula de memoria o la de referencia, es mayor. Sin embargo, dado que la diferencia en las corrientes de las celdas de memoria entre los estados 0 y 1 (la ventana de lectura) es menor en la MRAM que en la memoria flash, la corriente de referencia debe situarse con precisión en el centro de la ventana de lectura para que ésta sea más rápida. La nueva tecnología introduce dos mecanismos. El primero alinea la corriente de referencia en el centro de la ventana en función de la distribución real de la corriente de las celdas de memoria de cada chip medida durante el proceso de prueba. El otro mecanismo reduce la desviación del amplificador sensor. Con estos ajustes se consigue una mayor velocidad de lectura.

Además, en las configuraciones convencionales, hay una gran capacidad parásita en los circuitos utilizados para controlar la tensión de la línea de bits para que no suba demasiado durante las operaciones de lectura. Esto ralentiza el proceso de lectura, por lo que en este circuito se introduce un esquema de conexión Cascode (Nota 1) para reducir la capacitancia parásita y acelerar la lectura.

Gracias a estos avances, Renesas puede lograr el tiempo de acceso de lectura aleatoria más rápido del mundo, de 4,2 ns. Incluso teniendo en cuenta el tiempo de preparación del circuito de interfaz que recibe los datos de salida de la MRAM, podemos realizar la operación de lectura aleatoria a frecuencias superiores a 200 MHz.

(2) Tecnología de escritura rápida

Para la operación de escritura, las tecnologías de escritura de alta velocidad para STT-MRAM embebida anunciadas en diciembre de 2021 mejoraron el rendimiento de escritura aplicando primero tensión de escritura simultáneamente a todos los bits de una unidad de escritura utilizando una tensión de escritura relativamente baja generada a partir de la tensión externa (alimentación IO) del chip MCU a través de un circuito reductor, y utilizando después una tensión de escritura más alta sólo para los pocos bits restantes que no se podían escribir. Esta vez, Renesas tiene en cuenta que, dado que las condiciones de alimentación utilizadas en los procesos de prueba y por los fabricantes de productos finales son estables, el límite inferior de la tensión externa puede relajarse. De este modo, al establecer que se aplique a todos los bits de la primera fase la tensión de reducción más alta de la tensión externa, el rendimiento de escritura puede mejorarse 1,8 veces.

Combinando las nuevas tecnologías mencionadas, se fabricó un prototipo de chip de prueba MCU con una matriz de celdas de memoria MRAM de 10,8 Mbit utilizando un proceso MRAM embebido de 22 nm. La evaluación del chip prototipo confirmó que alcanzaba una frecuencia de acceso de lectura aleatoria superior a 200 MHz y un rendimiento de escritura de 10,4 MB/s a una temperatura máxima de unión de 125°C.

El chip de prueba también contiene 0,3 Mbit de OTP (Nota 2) que utiliza la ruptura de celdas de memoria MRAM para evitar la falsificación de datos. Esta memoria puede utilizarse para almacenar información de seguridad. La escritura en OTP requiere un voltaje más alto que la escritura en MRAM, lo que dificulta la escritura sobre el terreno, donde los voltajes de alimentación suelen ser menos estables. Sin embargo, al suprimir la resistencia parásita dentro de la matriz de celdas de memoria, esta nueva tecnología también hace posible la escritura sobre el terreno.

Renesas sigue desarrollando tecnologías para integrar MRAM en MCU (IEDM 2021, VLSI 2022). Estas nuevas tecnologías tienen el potencial de aumentar drásticamente la velocidad de acceso a la memoria a más de 200 MHz, permitiendo MCUs de mayor rendimiento con MRAM integrada. Una mayor velocidad de escritura contribuirá a una escritura de código más eficiente en los dispositivos finales. Renesas se compromete a seguir aumentando la capacidad, velocidad y eficiencia energética de la MRAM.

Notas

La conexión en cascada es una configuración para conectar un transistor de fuente común en serie a un transistor con una polarización de puerta de CC aplicada.

Memoria programable una sola vez. Configurar una parte de la matriz de memoria MRAM para convertirla en OTP permite implementar una OTP con un área menor que una macro OTP general que utilice eFuses o ruptura de la película de óxido de los transistores.

Articulos Electrónica Relacionados

- Equilibrio entre seguridad y c... Como respuesta al encarecimiento de los combustibles fósiles y a la preocupación por el medio ambiente está registrando un fuerte auge la instalación de paneles...

- Comprender la selección de con... En la última década, las naves espaciales en órbita terrestre se han convertido en grandes industrias con aplicaciones de gran consumo. Esto ha dado lugar al...

- Resistencias chip antisulfurac... ROHM acaba de anunciar la disponibilidad de nuevas resistencias chip antisulfuración optimizadas para aplicaciones expuestas a entornos ricos en sulfuro,...

- Diodos Schottky de carburo de ... Nexperia ha anunciado su entrada en el mercado de diodos de carburo de silicio (SiC) de alta potencia con la introducción de diodos Schottky de SiC de 650 V y 1...

- Condensadores cerámicos multic... Murata presenta condensadores cerámicos de 10uF (con una tolerancia del ±20%), que están disponible en un encapsulado de tamaño 0201’’/0603M en los MLCC de la s...

- Condensadores de película con ... TDK-EPC, una empresa del grupo de la TDK Corporation, ha desarrollado una amplia gama de condensadores película EPCOS MKP y MKT con bajas alturas de inser...

- Condensadores cerámicos multic... RS Components (RS) y Allied Electronics (Allied), marcas comerciales de Electrocomponents plc, distribuidor de productos y servicios de electrónica y mantenimie...

- Nueva serie de condensadores h... Avanzando en las especificaciones de rendimiento de las populares series ZT y ZC de condensadores híbridos electrolíticos de polímero, Panasonic Industry presen...

- Línea de conjuntos de cables c... La división de Interconexión de CUI Devices ha anunciado la introducción de conjuntos de cables circulares en su cartera de montajes cable-conector. Disponible ...

- Sistema de interruptores de se... El nuevo sistema de interruptores de seguridad de Phoenix Contact está compuesto por el interruptor de seguridad codificado y sin contacto PSRswitch y el...

- Ferrita partida con rango de t... KGS Kitagawa GmbH, distribuida en España y Portugal por RC Microelectrónica, presenta su ferrita partida cilíndrica para cables de hasta 18,5mm de diámetro de K...

- Componentes para protección de... ProTek Devices presenta su serie SM15KPAN de componentes de supresores de tensión momentánea (TVS, por sus siglas en inglés) de alta potencia y montaje superfic...