Historia y perspectiva de los convertidores A/D de aproximaciones sucesivas (SAR) de gran tensión y alto rendimiento

Las aplicaciones industriales a menudo se ven expuestas a duras condiciones ambientales. Las señales analógicas recorren grandes distancias por cable, de manera que el ruido de modo común y los campos electromagnéticos pueden afectar a las señal.

Las señales se vuelven más resistentes al ruido y a la distorsión cuando tienen mayor amplitud. Por eso el estándar industrial más extendido para el intervalo de señales analógicas es de ±10 V. En este artículo se explican las razones por las que los convertidores analógico-digital (ADC) por aproximación sucesiva (SAR) de la última generación no son compatibles con este intervalo de señales y por qué los ADC modernos están volviendo a este estándar.

Los ADC con un registro de aproximación sucesiva funcionan como una balanza [1, 2]. Como se muestra en la Figura 1, el comparador evalúa si la tensión de entrada Vin capturada por el condensador de muestreo y captura (S&H) es superior o inferior a la tensión generada por un convertidor digital-analógico capacitivo (DAC o CDAC). El DAC aproxima la tensión de entrada con un bit de precisión adicional por cada ciclo de reloj.

El ADC por SAR es el convertidor más utilizado, aunque no es el más rápido ni el de mayor precisión. La ventaja del ADC por SAR en comparación con el convertidor delta-sigma de alta resolución es la capacidad de tomar una muestra instantánea de la señal original, lo que permite muestrear la señal en un momento exactamente definido. En el control de procesos industriales, este aspecto a menudo es importante.

Es más, el ADC por SAR alcanza tasas de conversión más altas con una disipación de potencia semejante. Si se compara con los convertidores pipeline, el ADC por SAR ofrece un mejor rendimiento ante el ruido y consume mucha menos energía, aspecto de importancia en sistemas alimentados por baterías o en los que la disipación de potencia está limitada por la aplicación.

Las aplicaciones industriales a menudo se ven expuestas a duras condiciones ambientales, por lo que es preferible un intervalo de señal analógica amplio (±10V o más) para reforzar esta señal. Desgraciadamente, los procesos con semiconductores por lo general no son compatibles con este intervalo de tensiones debido a la tensión de ruptura de los transistores internos. Este artículo describe la historia del convertidor por SAR y las nuevas soluciones de alta tensión mediante procesos analógicos especiales, y presenta, además, el panorama de la próxima generación de productos.

Limitaciones de los ADC de alta tensión en la anterior generación

Limitaciones de los ADC de alta tensión en la anterior generación

Hasta mediados de los años noventa, los ADC permitían un intervalo de tensiones en la entrada bipolar de ±5 V ó ±10 V. Esto se lograba mediante procesos CMOS de 2 mm y 3 mm que incluían resistencias muy lineales. Un ejemplo típico es el ADS7809 de Burr-Brown. La tabla 1 muestra algunas especificaciones. La no linealidad diferencial (DNL) permite alcanzar un rendimiento de 16 bits reales, pero la velocidad de conversión es lenta y el consumo de energía elevado.

Esto se debe al tamaño del transistor necesario. La entrada del comparador, por ejemplo, requiere un par diferencial de bajo ruido. El ruido de los transistores MOS es una función de la transconductancia gm, que es en sí una función de la razón entre el ancho W y la longitud L del transistor y la corriente que lo atraviesa. La longitud mínima está limitada por el proceso, el ancho ha de ser grande y la corriente elevada.

El tamaño de los dispositivos causará además una capacidad parásita inherente. Por ejemplo, la capacidad de puerta de la segunda etapa de ganancia del comparador limitará la velocidad del primer par diferencial y por lo tanto limitará también la velocidad de conversión del comparador. Así pues, en el diseño de convertidor se debe llegar a un compromiso entre potencia, velocidad y ruido.

Los transistores de gran tamaño de la generación anterior de ADC requerían además un gran tamaño de la oblea, lo que ocasionaba un gran coste de producción de la oblea y un menor beneficio. Por otro lado, la baja velocidad generaba largos tiempos de prueba, por lo que los ADC de alto rendimiento resultaban costosos. El gran tamaño de la oblea también requería grandes formatos de encapsulado, como el encapsulado con doble fila (DIP) o el encapsulado SOIC de cuerpo ancho para montaje superficial. Por lo tanto, la investigación y el desarrollo de los ADC se apartaron de los diseños y procesos de alta tensión y se encaminaron hacia procesos CMOS con menor longitud de puerta.

La primera generación de 5 V

El primer ADC de 16 bits sobre un proceso de 5 V (el ADS8320 de Burr-Brown) fue considerado como producto del año en 1998. El rendimiento ante el ruido se mejoró gracias a la mejor gm de los transistores. La potencia se redujo notablemente debido al uso de una menor tensión de alimentación y a los condensadores parásitos más pequeños. Esto permitió el uso de los ADC por SAR en nuevas aplicaciones como equipos portátiles y alimentados por baterías, como los productos con pantalla táctil.

Desgraciadamente, el reducido tamaño del LSB (bit menos significativo) hacía que el convertidor fuese más sensible. Los diseños tuvieron que hacer frente a problemas térmicos y a cambios de encapsulado, por lo que la linealidad diferencial se redujo a 14-15 bits y la linealidad integral a 13-14 bits (véase también la Tabla 2).

La segunda generación de 5 V

Se diseñaron nuevas arquitecturas para crear productos más resistentes y disminuir el ruido y la potencia. Una de esas arquitecturas es la corrección dinámica de errores [3], que permite los errores durante las decisiones de bit de los bits más significativos (MSB), mientras el comparador está sometido a una fuerte carga y la fuente de referencia debe recargar grandes condensadores. Estos errores se corrigen durante las decisiones de LSB, cuando las señales de menor nivel reducen los efectos de asentamiento. De esta manera mejoró la linealidad de la segunda generación de ADCs por SAR sobre un proceso de 5 V.

Los nuevos diseños de referencia con condensadores de compensación externos [4] redujeron aún más la potencia. Un diseño optimizado del DAC mejoró el rendimiento ante el ruido. Con un ADS8329 de Texas Instruments (TI) se obtuvo una relación señal/ruido (SNR) de 93 dB a una velocidad de conversión de 1 MSPS y un consumo de 39 mW con una alimentación de 5 V o 15,5 mW con una alimentación de 2,7 V (véase la Tabla 3).

Se presentaron arquitecturas de ADCs completamente diferenciales (véase la Figura 2) como el ADS8482 de TI para multiplicar por dos el intervalo de entrada junto con el tamaño del LSB y la relación señal/ruido. Teóricamente se puede obtener una mejora de 6 dB. Si se aumenta la resolución a 18 bits se reduce aún más el ruido de cuantización, por lo que se puede alcanzar una relación señal/ruido de 100 dB.

Lamentablemente, continuar reduciendo la longitud del transistor no llevará necesariamente a una reducción del ruido. Esto se debe a que el ruido de transistor del comparador y de la referencia ya no es dominante. Al reducir la tensión de entrada. el parámetro que se vuelve dominante es el llamado ruido kT/C. Se trata de un ruido térmico generado durante el muestreo por la resistencia de conducción Ron del interruptor de entrada. La densidad de ruido de una resistencia nRon se describe en [5].

(1)

En la ecuación (1) k representa a la constante de Boltzmann y T a la temperatura absoluta. La banda de este ruido térmico está limitada por la resistencia de conducción del interruptor y la capacidad de muestreo Cs del ADC. El ancho de banda efectivo del ruido [5] se puede calcular de la siguiente manera:

(2)

La tensión eficaz (rms) del ruido de muestreo Vsrms es por lo tanto:

(3)

Según muestra la ecuación (3), el ruido de muestreo sólo depende del tamaño del condensador de muestreo. Al cambiar a un proceso más moderno en el que la longitud del transistor se reduce en un factor x, la tensión de alimentación máxima admitida se reduciría en ese mismo factor x. Esta menor tensión de alimentación reduciría el intervalo de tensiones de entrada y por lo tanto el tamaño de un LSB en ese mismo factor x. Si el ruido de muestreo debe permanecer constante con respecto a un LSB, el condensador de muestreo se debe aumentar por x2.

Esto no sólo provocaría un destacado aumento del tamaño de la oblea, sino que pondría en peligro el proceso de recarga de los condensadores del DAC desde una referencia negativa (casi siempre masa) a una referencia positiva. La recarga x2 veces de la capacidad a una tensión de referencia x veces menor aumentaría la corriente de referencia en un factor x. La potencia consumida se mantendría constante, ya que se mantendría una corriente x veces superior hasta una tensión de referencia x veces menor. La única ventaja provendría del diseño del comparador (véase la Figura 3).

No parece posible mejorar el rendimiento de manera notable reduciendo la longitud de la puerta. Los elementos clave en el diseño analógico se concentraban en el desarrollo de un nuevo proceso que mantenía la longitud del transistor en 0,5 - 0,6 mm y que añadía elementos muy particulares para productos analógicos de alto rendimiento.

Desarrollo del proceso analógico de alto rendimiento

Un punto muy importante lo constituyen las resistencias correctamente emparejadas, que además muestran una baja deriva con la temperatura a lo largo de su vida útil. Con estas resistencias se pueden diseñar convertidores digital-analógico R-2R de alto rendimiento, como el DAC8831 de TI. Si además el coeficiente de tensión de la resistencia es pequeño, es posible crear DACs en serie con una no linealidad integral muy baja, como el DAC8558 de TI.

Un sustrato metálico extremadamente bajo permite el diseño de complejas interfaces y funciones digitales. Los productos de la generación anterior tenían generalmente entradas o salidas muy sencillas en serie o en paralelo. Se añadieron nuevas funciones que se controlaban mediante un mapa de registros interno. Con la ayuda de «fusibles eléctricos» o «memorias programables una sola vez» se implementó una regulación eléctrica, controlada también por el mapa de registros. Algunos productos implementaron incluso diversas interfaces que se controlaban externamente mediante los pines.

Además, un proceso BiCMOS tiene buenos transistores bipolares, que resultan importantes para los diseños de amplificadores y de referencias. Semejante proceso requiere una capa N enterrada que aísla del sustrato un pozo P (véase la Figura 4). Como efecto secundario, estas zonas aisladas de pozo P se utilizan para aislar del sustrato el conjunto de transistores NCH. De esta manera, el sustrato se puede aislar del ruido de la circuitería digital y los sensibles circuitos analógicos se pueden aislar del ruido del sustrato general.

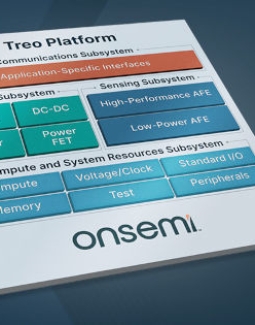

Los que resultan más interesantes son los transistores de alta tensión, que se implementan con un proceso de doble puerta. Entre el drenador y la fuente, al igual que entre la puerta y la fuente, se pueden aplicar 36 V. La mezcla de transistores de alta tensión y de baja tensión se puede utilizar para productos interesantes como la nueva generación de ADCs de alta tensión.

Una nueva generación de ADC de alta tensión

Aunque los ADC de 5 V alcanzan un excelente rendimiento ante el ruido, no son los más adecuados para el control de procesos industriales. Disponer de un convertidor de bajo ruido no es suficiente, ya que también se requiere una sección analógica resistente que se encargue de adecuar la señal entrante en estas duras condiciones. Las señales de entrada de ±10V automáticamente son cuatro veces más resistentes en comparación con los sistemas simples de 5 V. Es por esto que los ADCs de alta tensión continúan siendo de gran interés.

Una nueva generación de ADCs de alta tensión se beneficiará de los componentes del nuevo proceso. Existen dos enfoques. Uno de ellos consiste en utilizar las resistencias con la baja deriva y el bajo coeficiente de tensión. Se puede dividir y desplazar internamente la señal de entrada de ±10V al intervalo entre 0 y 5 V. Así la señal se puede procesar con transistores de 5 V y aprovechar la superior velocidad, menor ruido y menor consumo de estos transistores de baja tensión. Un ejemplo típico es el ADS8515 de TI. Sin embargo, el rendimiento se mejoró con nuevas arquitecturas y el nuevo proceso. En la Tabla 4 se comparan las especificaciones de la generación anterior (ADS7809) y la nueva generación (ADS8515).

Esta implementación presenta dos inconvenientes. En primer lugar se fuerza una corriente continua proveniente de la señal de entrada, por lo que las fuentes de entrada de alta impedancia generarán errores de ganancia. Para mantener esta corriente baja es necesario que la resistencia interna sea alta, lo que limita el ancho de banda de la entrada del ADC. Esto exige de manera automática tiempos de muestreo más prolongados, lo que ocasiona velocidades de conversión más bajas.

En el segundo enfoque, la señal de entrada de alta tensión se muestrea directamente en el condensador de muestreo mediante transistores de alta tensión. A continuación, el DAC capacitivo del ADC por SAR divide la señal. Este método también presenta desventajas.

Aunque los condensadores ofrezcan un excelente coeficiente de tensión, seguirá afectando a la linealidad integral del ADC. A alta tensión esto resulta especialmente cierto para el coeficiente cuadrático de tensión. Si una señal de 10 V se almacena en el condensador y el coeficiente cuadrático de tensión es aproximadamente 1 ppm/V2, la variación del condensador de muestreo es de 100 ppm en los extremos, pero no en el centro de la escala. La no linealidad integral alcanza a varios LSB.

El segundo inconveniente está causado por la alta resistencia de conducción Ron y la alta capacidad parásita Cmsw de los interruptores de entrada de alta tensión. Ambos efectos son no lineales respecto a la tensión de entrada y no afectan al rendimiento en CC. No obstante, las señales de CA se ven afectadas por la distorsión debida al retardo Ron·(Csw+Cs) de la circuitería de muestreo que depende de la tensión de entrada. La inicialización (véase la Figura 5), donde la puerta del interruptor de entrada tiende hacia la señal de entrada más una tensión constante y donde el conjunto está cortocircuitado con la entrada, permite reducir la distorsión armónica total, pero requiere mucha circuitería y aumenta el tamaño de la oblea.

Sin embargo, el muestreo con conmutadores de alta tensión parece ser la técnica que se utilizará en los productos futuros. Se desarrollarán nuevas arquitecturas de diseño y otras mejoras en el proceso para superar los problemas mencionados.

Perspectivas

En resumen, los nuevos productos de alta tensión proporcionan mejoras significativas en lo que respecta a la velocidad, la potencia y el ruido. Lamentablemente sigue habiendo dos limitaciones principales. El interruptor de muestreo de alta resistencia, que además presenta una notable capacidad parásita, afecta a la distorsión armónica total (THD) a frecuencias de señal superiores a 100 kHz. Además, el coeficiente de tensión del condensador genera una no linealidad integral independiente de la frecuencia de entrada.

Al parecer, se requieren avances adicionales para solucionar el problema de la THD. Por otro lado, es hora de desarrollar una solución de regulación para la no linealidad integral, sobre todo porque todas las demás especificaciones de CC son ajustables, como la no linealidad diferencial, el desplazamiento [6], la ganancia [7] e incluso el rechazo de modo común.

Asimismo, la alta tensión de entrada debería posibilitar diseños que mejoren el rendimiento ante el ruido en el ámbito de la relación señal/ruido. Es previsible que en el futuro aparezcan productos con una relación de 106 dB.

Referencias

[1] F. Oehme, M. Huemer and M. Pfaff, Elektronik und Schaltungstechnik, Carl Hanser Verlag, ISBN 3-446-40694-8, 2006.

[2] Rudy J. van de Plassche, CMOS Integrated Analog-to-Digital and Digital-to-Analog Converters, Springer Netherlands, ISBN 1-4020-750-6, 2003.

[3] Chakravarthy Srinivasean, Kiran M. Godbole, Error correction architecture to increase speed and relax current drive requirements of SAR ADC, patente US6747589, Texas Instruments, 2004.

[4] Frank Ohnhaeuser, Mario Huemer, Reference generation for A/D converters, actas sobre CD-ROM del Simposio internacional sobre señales, sistemas y electrónica (ISSSE2007), Montreal (Canadá), agosto de 2007.

[5] P. Gray, R. Meyer, Analysis and Design of ANALOG INTEGRATED CIRCUITS, John Wiley & Sons, Inc., ISBN 0-471-57495-3, 1993.

[6] Frank Ohnhaeuser, Miroslav Oljaca, Offset error compensation of input signals in analog-to-digital converter, patente US6433712, Texas Instruments, 2002.

[7] Robert Seymour, Method and circuit for gain and/or offset correction in a capacitor digital-to-analog converter, Patente US6922165, Texas Instruments, 2005.

Autor:

Frank Ohnhaeuser. Texas Instruments

Articulos Electrónica Relacionados

- Convertidores DC/DC de 1W alto... Los nuevos TRI 1 y TRI 1SM son una serie de convertidores DC/DC regulados de alto aislamiento dispuestos en una carcasa compacta SIP-8 y SMD-14. La característi...

- Convertidores Mean Well DDR-15... MEAN WELL, representada por Electrónica OLFER, presenta su línea de convertidores CC/CC para montaje en carril DIN: la familia DDR, con la finalid...

- Convertidor CC-CC AMV TWIN 200... AMV lanza al mercado un nuevo formato de las series SD1000, RSP1000 y RSP2000. De esta manera, la gama de convertidores de AMV se incrementa en más de 24...

- Convertidores médicos CC/CC ME... Electrónica OLFER presenta las nuevas versiones para 15W y 20W de la serie MDS01/02 de MEAN WELL, las nuevas MDS15/20. Las principales características de estas ...

- Convertidores CC-CC aislados d... ROHM ha desarrollado recientemente un convertidor CC-CC flyback aislado, BD7Fx05EFJ-C (BD7F105EFJ-C, BD7F205EFJ-C) optimizado para fuentes de alimentación de co...

- Convertidores CC/CC SIP-8 de 1... P-DUKE ha ampliado su línea de convertidores CC/CC encapsulados SIP-8 diseñados específicamente para ferrocarriles, que ahora ofrecen hasta 10W de potencia de s...

- Convertidores miniatura DC/DC ... XP Power distribuido en España y Portugal por Venco Electronica, S.A., anuncia las series IML02 y ISM02, convertidores miniatura DC/DC de 2 W para ...

- Convertidor diseñado a partir ... El fabricante guipuzcoano de sistemas ferroviarios CAF Power & Automation y el centro tecnológico IK4-IKERLAN han desarrollado un innovador sistema d...

- Semikron mejora su convertidor... Semikron, mejora su SEMISTACK_RE, un módulo inteligente, IPM, para energías renovables (RE). El nuevo convertidor ha sido diseñado para ser usado en generadores...

- Convertidores CC/CC de 3 vatio... La nueva serie RI3 de convertidores CC/CC de 3 vatios de la marca RECOM se destaca por su tamaño especialmente compacto y su alta densidad de potencia. A...

- Convertidor CC/CC de 204 W y e... Murata Power Solutions lanza al mercado la serie UWQ de convertidores CC/CC de 204 W y chasis abierto en formato 1/4 brick y montaje through-hole. Con unas...

- Convertidor CC-CC de grado méd... CUI Inc, una empresa del grupo Bel, ha anunciado el lanzamiento de su serie PTP15, un convertidor CC-CC aislado DIP de 15 W y 5 patillas, especializado para ins...