Los periféricos inteligentes ayudan a automatizar tareas de bajo nivel en sistemas de microcontroladores

La familia RA de microcontroladores ARM Cortex de Renesas se basa en la rica historia de los microcontroladores Renesas anteriores, como las muy populares familias H8 o M16C. La familia RA utiliza o mejora muchas de las funciones periféricas que se implementaron originalmente en estos dispositivos. Estos periféricos han sido probados durante muchos años y proporcionan un funcionamiento probado y predecible, algunos también proporcionan características únicas que pueden mejorar el rendimiento de una aplicación o reducir el consumo de energía.

En este artículo veremos cómo funcionan algunos de estos periféricos y cómo pueden combinarse para automatizar muchas de las tareas de bajo nivel que deben gestionarse en una aplicación típica de microcontrolador.

Probablemente uno de los periféricos más interesantes pero menos comprendidos dentro de un microcontrolador RA típico, es el DOC - Data Operations Circuit (Circuito de Operaciones de Datos). Éste puede proporcionar importantes ventajas de rendimiento en aplicaciones en tiempo real, permitiendo descargar tareas sencillas de la CPU, mejorando el tiempo de respuesta y reduciendo potencialmente el consumo de energía. Esto es especialmente cierto cuando el DOC se utiliza junto con otras funciones más avanzadas disponibles en la familia RA.

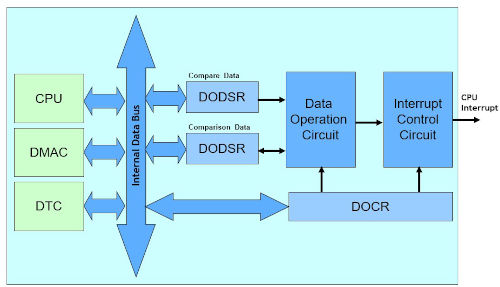

En el corazón del DOC se encuentra una sencilla ALU - Arithmetic Logic Unit (unidad aritmética lógica). Esta ALU simple tiene sólo tres funciones básicas, puede hacer una comparación de datos de 16 bits, una suma de 16 bits, o una resta de 16 bits, y luego generar una interrupción basada en una condición especificada. Todas estas tareas pueden ser ejecutadas sin ninguna intervención de la CPU mediante la transferencia automática de los datos a ser operados por el DOC, utilizando un controlador DMA o el controlador de Transferencia de Datos, que explicaremos en un momento. Véase la figura 1.

Figura 1: Diagrama de bloques simplificado del Circuito de Operación de Datos (DOC)

Cuando se utiliza el modo de comparación de 16 bits, se carga un valor de referencia inicial en el DOC, a continuación, se cargan los datos de 16 bits que se van a comparar y se comparan con el valor de referencia en hardware. El DOC puede programarse para generar una interrupción en caso de coincidencia verdadera o falsa.

Cuando se utiliza el modo de suma de 16 bits, se carga un valor inicial de 16 bits en el DOC, a continuación, se cargan valores adicionales de 16 bits (pueden ser uno o varios) en el DOC y se suman al valor original. Cuando se han cargado todos los valores necesarios, se comprueba si el recuento se ha desbordado y, en caso necesario, se genera una interrupción. Este sencillo mecanismo permite decidir si se ha superado un valor umbral específico, ideal, por ejemplo, para la detección automática de nivel mediante el ADC.

Cuando se utiliza el modo de sustracción de 16 bits, se carga un valor inicial de 16 bits en el DOC, a continuación, se cargan valores adicionales de 16 bits (pueden ser uno o varios) en el DOC y se restan del valor original. Cuando se han cargado todos los valores necesarios, se comprueba que no haya desbordamiento y, si es necesario, se genera una interrupción. De nuevo, este sencillo mecanismo permite decidir si se ha superado un valor umbral específico.

Sin embargo, el verdadero poder del Circuito de Operación de Datos está en el hecho de que estas tres simples funciones pueden ser usadas para tomar decisiones simples sobre cómo funcionará el sistema, sin ninguna intervención de la CPU. Esto significa que podemos tomar decisiones simples, directamente en el hardware del microcontrolador, permitiendo que el hardware del sistema decida cómo gestionar los datos que producen basándose en una simple comparación.

Cuando se combina con periféricos como el DMAC - Direct Memory Access Controller (Controlador de Acceso Directo a Memoria) o el DTC - Data Transfer Controller (Controlador de Transferencia de Datos), que se pueden utilizar para automatizar el paso de datos al DOC, podemos ver cómo esto se puede utilizar para crear un sistema capaz de tomar decisiones basadas en datos de casi cualquier fuente. Esto puede hacerse sin ninguna intervención de la CPU, incluso cuando la CPU está en reposo. Esto puede proporcionar una respuesta mucho más rápida a los datos cambiantes, en lugar de esperar a que la CPU se interrumpa para luego responder al evento.

Podemos imaginar muchos casos en los que el DOC podría ser utilizado, por ejemplo, cuando se utiliza con la interfaz UART, el DOC podría ser utilizado para detectar automáticamente una dirección entrante y alertar a la CPU cuando la dirección es válida. El DOC podría utilizarse con el convertidor analógico-digital (ADC) en un sistema de detección de nivel, para detectar automáticamente cuando el nivel supera un umbral programado. El uso del DOC para este tipo de funciones tiene muchas ventajas. Por ejemplo, la CPU podría dedicarse a otras tareas de alta prioridad, y el DOC sólo avisaría, mediante una interrupción, cuando se alcanzara una determinada condición. La CPU puede ponerse en reposo, para reducir el consumo de energía, y sólo despertarse de nuevo mediante una interrupción en una condición de alarma válida detectada por la comparación DOC.

Puede encontrar el Circuito de Operación de Datos en todos los miembros de la familia RA, y hemos seguido mejorando las funciones del DOC y las últimas versiones tienen funciones adicionales que permiten tomar decisiones aún más complejas sobre los datos de forma automática.

Veamos ahora el Controlador de Transferencia de Datos (DTC) que hemos mencionado antes. Se trata de un periférico que ha sido diseñado para proporcionar un mecanismo sencillo, pero extremadamente flexible, para transferir datos entre un periférico y la memoria o la memoria y un periférico. Se puede encontrar un Controlador de Transferencia de Datos en todos los miembros de la familia de microcontroladores RA.

El DTC utiliza un simple controlador programable para realizar transferencias de datos entre la memoria y los periféricos, y viceversa, manteniendo su información de configuración en una tabla en SRAM. Esto es mucho más pequeño que utilizar un gran bloque de hardware dedicado para esta tarea, como el que suele utilizar el Controlador de Acceso Directo a Memoria (DMAC). Esta programabilidad nos proporciona un nivel de flexibilidad mucho mayor en comparación con el uso de un DMAC, y al almacenar la tabla de configuración que describe la transferencia en SRAM podemos tener canales casi ilimitados, sólo restringidos por la cantidad disponible de SRAM.

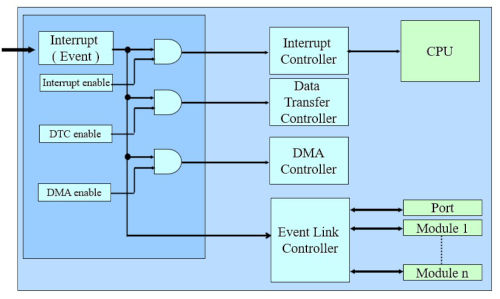

En la familia RA, un evento (o interrupción), disparado por la CPU, por un periférico en el dispositivo, o por un pin externo puede generar varias acciones en el dispositivo. Puedes ver un diagrama simplificado del controlador de interrupciones en la figura 2, aquí puedes ver que un evento puede desencadenar varias acciones, una interrupción tradicional, que cambia la dirección de la aplicación, una transferencia DMAC, o una transferencia DTC, también es posible desencadenar más de una de estas desde un único evento.

Figura 2: Diagrama simplificado del controlador de interrupciones RA

L

a principal ventaja de esta programabilidad es que contiene toda la información necesaria para la transferencia en un pequeño bloque de SRAM en el chip. Esto significa que el controlador DTC puede utilizarse no sólo para crear uno o dos canales de transferencia de datos, sino 10, 20 o incluso más si es necesario. La principal desventaja de este mecanismo es que cada transferencia requiere unos cuantos ciclos de lectura de los datos de configuración almacenados en la SRAM, por lo que la transferencia DTC suele ser más lenta que una transferencia DMA.

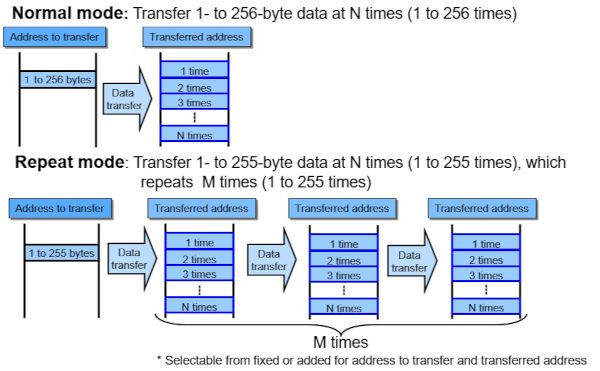

El DTC puede transferir 1 byte o más de un byte, entre un periférico y la memoria o la memoria y el periférico hasta 256 veces. La dirección de origen y la de destino de la transferencia pueden ser la misma dirección o incrementarse o decrementarse independientemente, creando así una estructura de búfer en la memoria.

Al final de la transferencia, el DTC puede generar una interrupción, para indicar a la CPU que los datos están listos, o puede activar una segunda transferencia DTC. Esto puede utilizarse para encadenar varias transferencias, y es lo que llamamos, curiosamente, modo cadena. Este modo de cadena puede ser especialmente útil si se requiere el movimiento de múltiples piezas de datos entre los periféricos y la memoria. El modo cadena es particularmente interesante cuando se utiliza con el DOC que hemos discutido anteriormente, ya que esto significa que múltiples transferencias desde varias ubicaciones en memoria y/o periféricos pueden ser activadas por una fuente de interrupción. Por ejemplo, esto significa que, con una interrupción, como la interrupción del ADC, podemos hacer que los datos de comparación se carguen en el DOC, y encadenando una segunda transferencia, podemos cargar el DOC con los datos del ADC para ser comparados, todo de forma completamente automática, sin intervención de la CPU. Esta capacidad de una interrupción para generar una secuencia compleja de diferentes transferencias es extremadamente potente, no sólo cuando se utiliza con el DOC. En la figura 3 se muestran algunos de los diferentes modos de funcionamiento del DTC.

Figura 3: Ejemplos de modos de funcionamiento del controlador de transferencia de datos

El DTC también puede ponerse en modo de repetición, en el que repetirá la transferencia un número adicional de veces. Para la mayoría de las aplicaciones, la flexibilidad del DTC ofrece un equilibrio perfecto entre velocidad, flexibilidad y, por supuesto, coste del dispositivo. Se pueden crear transferencias automatizadas entre cualquier periférico y memoria casi sin límite.

El Controlador de Transferencia de Datos proporciona un método ideal para automatizar la transferencia de datos entre periféricos y memoria, sin intervención de la CPU. El uso del DTC en modo cadena al transferir datos al DOC, nos proporciona la capacidad de realizar pruebas sencillas sobre muchos datos sin intervención de la CPU, proporcionando así al propio chip la capacidad de tomar decisiones sencillas.

Esperemos que puedas ver cómo el DTC puede ser mucho más flexible que el DMAC tradicional, si necesitas las más altas velocidades de transferencia de datos, el DMAC sigue siendo el método más apropiado y casi todos los microcontroladores RA incluyen un número de canales DMAC, pero por flexibilidad, y la forma en que puedes gestionar los datos el DTC gana por goleada en flexibilidad, y puedes crear múltiples canales, sólo limitados por la SRAM disponible.

Veamos ahora cómo se pueden combinar el DTC y el DOC con el ADC para crear un sistema de muestreo analógico inteligente que pueda funcionar completamente sin intervención de la CPU, reduciendo así potencialmente la demanda de la CPU e incluso ahorrando consumo de energía al apagar la CPU mientras el sistema funciona. El sistema que queremos crear es un simple detector de nivel de entrada múltiple, que utiliza el modo de barrido de grupo del ADC de 12 bits para muestrear cada una de las 4 señales de entrada sucesivamente y utilizando la combinación del DTC y el DOC, detecta si se supera un nivel umbral programable, y sólo si se ha superado este valor, el sistema generará una interrupción y despertará a la CPU.

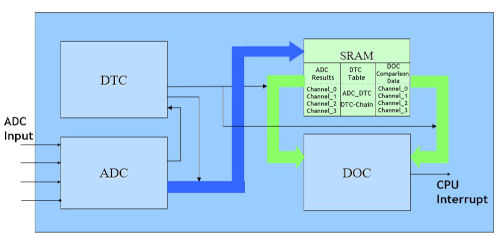

Tras la configuración inicial del sistema, la CPU entra en reposo para ahorrar energía, y sólo se despierta si se produce una interrupción del DOC, indicando que se ha superado el umbral. En la figura 4 se muestra un esquema simplificado del sistema.

Figura 4: Diseño simplificado del sistema

Figura 4: Diseño simplificado del sistema

I En el modo de barrido en grupo, el ADC muestrea continuamente cada entrada por turno y copia el resultado en la SRAM. Cuando las 4 entradas han sido muestreadas, el ADC genera una petición DTC. Utilizando el modo cadena, esta petición inicia una cadena de 8 transferencias entre la memoria y el DOC, copiando de la SRAM en chip, tanto los 4 resultados del ADC, como un valor umbral correspondiente con el que cada resultado del ADC debe ser comparado de nuevo.

Petición de transferencia del ADC al DTC..

DTC transferencia 1 Comparación[0] a DOC. Cadena Activada, se realiza la siguiente transferencia

DTC transferencia 2 AN000 a DOC Cadena Activada, se realiza la siguiente transferencia

DTC transferencia 3 Comparación[0] a DOC Cadena Activada, se realiza la siguiente transferencia

DTC transferencia 4 AN001 a DOC Cadena Activada, se realiza la siguiente transferencia

DTC transferencia 5 Comparación[0] toa DOC Cadena Activada, se realiza la siguiente transferencia

DTC transferencia 6 AN003 a DOC Cadena Activada, se realiza la siguiente transferencia

DTC transferencia 7 Comparación[0] a DOC Cadena Activada, se realiza la siguiente transferencia

DTC transferencia 8 AN005 to DOC Cadena desactivada, parada

En este caso, inicializamos el DOC para comparar cada valor y generar una interrupción si se supera alguno de los valores umbral.

Una vez inicializados el ADC, el DOC y el DTC, cada entrada del ADC se comprueba continuamente en segundo plano, sin intervención de la CPU. La CPU puede gestionar otras tareas o ponerse en reposo y no se despertará hasta que una de las entradas supere el valor correspondiente.

Muchas otras tareas de bajo nivel pueden automatizarse mediante la combinación de DOC y DTC de forma muy similar. Esta puede ser una técnica extremadamente potente para automatizar funciones de bajo nivel y puede ahorrar tiempo y costes de desarrollo en el desarrollo de controladores de software de bajo nivel para estas tareas, así como mejorar el rendimiento del sistema mediante la automatización de las funciones básicas sin la necesidad de ninguna participación de la CPU.

Cada miembro de la familia de microcontroladores RA incluye funciones periféricas inteligentes como el Circuito de Operación de Datos y el Controlador de Transferencia de Datos junto con muchas otras funciones periféricas de potencia que también pueden utilizarse para crear subsistemas inteligentes. Juntos, el DOC y el DTC proporcionan soluciones muy flexibles y potentes para automatizar funciones de E/S de bajo nivel en muchas aplicaciones diferentes. La automatización de estas funciones de bajo nivel no sólo mejora el tiempo de respuesta del sistema a eventos en tiempo real, sino que a menudo puede reducir la complejidad y el tamaño del software del sistema, aumentando así la fiabilidad y reduciendo los costes de las pruebas del sistema.

La familia de microcontroladores RA está destinada a una amplia gama de aplicaciones de comunicaciones y control, como control de motores, sensores inteligentes, medición, instrumentos portátiles, módems de bajo consumo y muchas otras aplicaciones industriales y de consumo, y se presenta en una amplia gama de opciones de tamaño de memoria y encapsulado. Para más información, visite www.renesas.com/ra.

Autor: Graeme Clark, Especialista principal en marketing de productos, Renesas Electronics

Articulos Electrónica Relacionados

- Microcontroladores de 32 bit P... Microchip anuncia una nueva serie dentro de su familia de microcontroladores de 32 bit PIC32MX1/2 que incorpora una configuración de 256 KB de Flash y 16...

- Microcontroladores Microchip A... Ayudar a los ingenieros a cubrir los exigentes requisitos de seguridad minimizando los costes y la complejidad del sistema ha llevado a Microchip Technology a p...

- Microcontroladores tinyAVR® de... Microchip Technology Inc. anuncia la ampliación de su serie de microcontroladores tinyAVR® con dos nuevos dispositivos que ofrecen funciones an...

- Virtualización Segura en Micro... Green Hills Software acaba de anunciar la disponibilidad de µ-visor™, su hipervisor de virtualización para el micontrolador (MCU) Renesas RH850/UA2. µ-visor par...

- Microcontroladores MCX de NXP ... Mouser Electronics, Inc ya distribuye los microcontroladores (MCU) industriales y de IoT MCX de NXP Semiconductors. Estos MCU nuevos son microcontroladores de a...

- MCU Renesas RA2A2 con soporte ... Renesas Electronics Corporation ha presentado hoy el grupo de microcontroladores (MCU) RA2A2 basado en el procesador Arm® Cortex®-M23. Los nuevos dispositivos, ...

- Nuevos microcontroladores Micr... El ámbito del diseño embebido, dominado en 2022 por los smartphones, los vehículos autónomos y la conectividad inalámbrica 5G, las familias de microcontroladore...

- La gama RX230 amplía la serie ... Renesas Electronics Europe presenta la nueva gama de microcontroladores (MCUs) RX230 de 32 bits, que ofrece una combinación óptima de alto rendimi...

- MCU NuMicro® M2354 para servid... Nuvoton Technology lanza el NuMicro® M2354 mejorado, diseñado para aplicaciones como RoT para servidores, ciudades inteligentes, IoT y medición inteligente. NuM...

- Una tecnología que abarca las ... Los expertos del sector sanitario creen que deben cambiar muchas cosas para afrontar los retos de la vida moderna. Los dos retos principales son el hecho de que...

- Microcontrolador Renesas R9A02... Mouser ya tiene en stock los microcontroladores (MCU, por sus siglas en inglés) de baja potencia R9A02G021 de Renesas Electronics. El R9A02G021, que ofrece a lo...

- MCUs Renesas RA6M4 para aplica... Mouser Electronics, Inc ofrece los nuevos microcontroladores RA6M4 de 32 bits de Renesas Electronics. Los microcontroladores RA6M4 aceleran el desarrollo de los...