Acelerador de IA para modelos ligeros de IA y tecnología de procesador embebido para permitir el procesamiento en tiempo real

Renesas Electronics Corporation ha anunciado el desarrollo de tecnología de procesador embebido que permite mayores velocidades y menor consumo de energía en unidades de microprocesador (MPU) que implementan IA de visión avanzada. Las tecnologías desarrolladas son las siguientes:

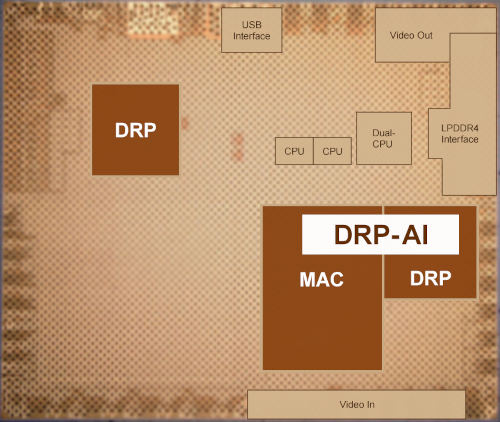

(1) un acelerador de IA basado en un procesador dinámicamente reconfigurable (DRP) que procesa de manera eficiente modelos de IA livianos y (2) tecnología de arquitectura heterogénea que permite el procesamiento en tiempo real mediante IP de procesador que operan de manera cooperativa, como el UPC. Renesas produjo un prototipo de AI-MPU integrada con estas tecnologías y confirmó su funcionamiento de alta velocidad y bajo consumo de energía. Logró un procesamiento hasta 16 veces más rápido (130 TOPS) que antes de la introducción de estas nuevas tecnologías, y una eficiencia energética de clase mundial (hasta 23,9 TOPS/W con un suministro de 0,8 V).

En medio de la reciente proliferación de robots en fábricas, logística, servicios médicos y tiendas, existe una necesidad creciente de sistemas que puedan funcionar de forma autónoma en tiempo real detectando el entorno mediante IA de visión avanzada. Dado que existen severas restricciones en la generación de calor, particularmente para dispositivos embebidos, en los chips de IA se requieren tanto un mayor rendimiento como un menor consumo de energía.

Las tecnologías desarrolladas por Renesas son las siguientes:

Un acelerador de IA que procesa eficientemente modelos de IA ligeros

Como tecnología típica para mejorar la eficiencia del procesamiento de IA, la poda está disponible para omitir cálculos que no afectan la precisión del reconocimiento. Sin embargo, es común que en los modelos de IA existan cálculos que no afectan la precisión del reconocimiento de forma aleatoria. Esto provoca una diferencia entre el paralelismo del procesamiento del hardware y la aleatoriedad de la poda, lo que hace que el procesamiento sea ineficiente.

Para resolver este problema, Renesas optimizó su exclusivo acelerador de IA basado en DRP (DRP-AI) para la poda. Al analizar cómo las características del patrón de poda y un método de poda se relacionan con la precisión del reconocimiento en modelos típicos de IA de reconocimiento de imágenes (modelos CNN), identificamos la estructura de hardware de un acelerador de IA que puede lograr tanto una alta precisión de reconocimiento como una tasa de poda eficiente, y aplicamos al diseño DRP-AI. Además, se desarrolló un software para reducir el peso de los modelos de IA optimizados para este DRP-AI. Este software convierte la configuración del modelo de poda aleatoria en computación paralela altamente eficiente, lo que resulta en un procesamiento de IA de mayor velocidad. En particular, la tecnología de soporte de poda altamente flexible de Renesas (tecnología de poda flexible N:M), que puede cambiar dinámicamente el número de ciclos en respuesta a cambios en la tasa de poda local en los modelos de IA, permite un control preciso de la tasa de poda según el consumo de energía, la velocidad de funcionamiento y la precisión de reconocimiento requeridos por los usuarios.

Esta tecnología reduce la cantidad de ciclos de procesamiento de modelos de IA a tan solo una decimosexta parte de la poda de modelos incompatibles y consume menos de una octava parte de la energía.

Tecnología de arquitectura heterogénea que permite el procesamiento en tiempo real para el control de robots

Las aplicaciones robóticas requieren un procesamiento avanzado de IA de visión para el reconocimiento del entorno circundante. Mientras tanto, el juicio y el control del movimiento del robot requieren una programación detallada de las condiciones en respuesta a los cambios en el entorno, por lo que el procesamiento de software basado en CPU es más adecuado que el procesamiento basado en IA. El desafío ha sido que las CPU con procesadores integrados actuales no son completamente capaces de controlar robots en tiempo real. Es por eso que Renesas introdujo un procesador dinámicamente reconfigurable (DRP), que maneja procesamiento complejo, además de la CPU y el acelerador de IA (DRP-AI). Esto llevó al desarrollo de una tecnología de arquitectura heterogénea que permite mayores velocidades y un menor consumo de energía en las AI-MPU mediante la distribución y paralelización de procesos de manera adecuada.

Un DRP ejecuta una aplicación mientras cambia dinámicamente la configuración de conexión del circuito entre las unidades aritméticas dentro del chip para cada reloj de operación de acuerdo con los detalles del procesamiento. Dado que, incluso en procesos complejos, sólo funcionan los circuitos aritméticos necesarios, es posible un menor consumo de energía y mayores velocidades. Por ejemplo, SLAM (localización y mapeo simultáneos), una de las aplicaciones robóticas típicas, es una configuración compleja que requiere múltiples procesos de programación para el reconocimiento de la posición del robot en paralelo con el reconocimiento del entorno mediante el procesamiento de IA visual. Renesas demostró el funcionamiento de este SLAM mediante la conmutación instantánea de programas con el DRP y el funcionamiento paralelo del acelerador de IA y la CPU, lo que da como resultado velocidades de funcionamiento aproximadamente 17 veces más rápidas y aproximadamente 12 veces mayor eficiencia energética operativa que la CPU integrada sola.

Verificación de operación

Renesas creó un prototipo de chip de prueba con estas tecnologías y confirmó que logró la eficiencia energética más alta de clase mundial de 23,9 TOPS por vatio con un voltaje de alimentación normal de 0,8 V para el acelerador de IA y una eficiencia energética operativa de 10 TOPS por vatio. para los principales modelos de IA. También demostró que el procesamiento de IA es posible sin ventilador ni disipador de calor.

La utilización de estos resultados ayuda a resolver la generación de calor debido al mayor consumo de energía, que ha sido uno de los desafíos asociados con la implementación de chips de IA en una variedad de dispositivos integrados, como robots de servicio y vehículos guiados automáticamente. Reducir significativamente la generación de calor contribuirá a la expansión de la automatización en diversas industrias, como los mercados de la robótica y la tecnología inteligente. Estas tecnologías se aplicarán a la serie RZ/V de Renesas: MPU para aplicaciones de visión artificial.

Articulos Electrónica Relacionados

- Módulo de mini-cámara ultra-co... Suyin Optronics ofrece un módulo de cámara altamente miniaturizada que con la referencia de pieza CM 8013 AF05 OV01, que cuenta con una resolución máxima de 8 m...

- Aisladores digitales de 1 a 6 ... Mecter, distribuidor oficial de HopeRF para España y Portugal, anuncia el lanzamiento de sus aisladores digitales. La tecnología de aislamiento digital se reali...

- Procesadores Intel® Xeon® E7 v... Intel presenta la familia de productos E7-8800/4800 v3 del procesador Intel® Xeon® que aporta conocimiento empresarial acelerado a través de herramientas analít...

- Temporizadores con el menor Ji... Silicon Labs presenta las soluciones de temporización con frecuencia más flexible que ofrecen el mejor rendimiento jitter para networking de alta velocidad, com...

- Dispositivos MAC-PHY LAN8650/1... Microchip Technology amplía su catálogo de soluciones Ethernet certificadas para automoción y anuncia la nueva familia de dispositivos MAC-PHY LAN8650/1 certif...

- TFT 5,7” 640x480 LVDS Monolitic y Powertip han desarrollado para los mercados español y portugués una nueva versión de la TFT de 5,7 pulgadas VGA. La particularidad de este modelo es...

- Sensor monocapa verdadero con ... Cypress Semiconductor Corp. presenta el primer sensor monocapa del mercado para pantalla táctil con capacidad multitáctil. El nuevo sensor SLIM® (Single-Layer I...

- Sensor de efecto Hall digital ... Melexis Technologies NV presenta un nuevo sensor de efecto Hall digital y programable. El MLX92232 incorpora memoria EEPROM que permite establecer niveles de um...

- Optoacopladores de alta veloci... Toshiba Electronics Europe ha lanzado dos nuevos optoacopladores de alta velocidad, TLP 2745 y TLP 2748. Los nuevos optoacopladores CI de salida disponen de baj...

- SoC de interfaz de sensor de p... Mouser ya tiene en stock el sistema en chip (SoC) de interfaz de sensor de precisión de baja potencia MAX40109 de Analog Devices, Inc. (ADI). El SoC MAX40109 in...

- Rectificadores de Germanio de ... Nexperia, el experto en semiconductores esenciales, ha anunciado una gama de nuevos rectificadores de Germanio de Silicio (SiGe) con voltajes inversos de 120 V,...

- Temporizadores buffer de 1,5 V... Integrated Device Technology, Inc. (IDT ®) presenta la ampliación de su cartera de sincronización PCIe, con la primera familia de buffers PCI Express (PCIe®) de...