Tendencias de encapsulado de semiconductores avanzados en IA y HPC

Las tecnologías avanzadas de encapsulado de semiconductores, como la unión híbrida 2,5D y 3D, junto con soluciones emergentes como la fotónica de silicio, son fundamentales para optimizar el rendimiento del sistema y fomentar la próxima ola de innovación en chips de IA y HPC. El informe "Advanced Semiconductor Packaging 2024-2034: Forecasts, Technologies, Applications" (Embalaje avanzado de semiconductores 2024-2034: previsiones, tecnologías y aplicaciones), publicado por IDTechEx, explora el cambiante panorama del encapsulado de semiconductores, con especial atención al embalaje híbrido 2,5D y 3D.

Abarca las tendencias tecnológicas, los retos de la industria y los avances realizados por los principales actores, al tiempo que pronostica las tendencias del mercado en el sector del envasado de semiconductores.

Retos de los grandes modelos lingüísticos (LLM-Large Language Models):

La aparición de los grandes modelos lingüísticos (LLM) marca un hito en la IA, revolucionando el procesamiento del lenguaje natural (PLN) y campos afines. Modelos como la serie GPT de OpenAI demuestran una gran precisión a la hora de comprender, generar y traducir el lenguaje humano. Aunque encuentran diversas aplicaciones, también presentan retos.

Los LLM han experimentado un crecimiento exponencial en el tamaño del modelo, pasando de 340 millones de parámetros en BERT-L en 2019 a 1,76 billones de parámetros en el próximo GPT-4. Esta expansión se traduce en una alta complejidad computacional, ya que GPT-4 requiere más de 1010 petaFLOPS. En comparación con otras redes neuronales, las LLM exigen muchos más recursos computacionales; por ejemplo, el entrenamiento de la GPT-3 requiere 3841 horas de GPU frente a las 11 horas de una ResNet-60 (una red neuronal convolucional utilizada para la clasificación de imágenes). Las LLM tienen una intensidad operativa baja, lo que significa que dependen en gran medida de operaciones matriciales-vectoriales. Esto requiere mover más datos para realizar el mismo número de operaciones aritméticas. Por tanto, el ancho de banda de la memoria es fundamental para su rendimiento.

Formas de mejorar el ancho de banda del sistema:

En los últimos años, se ha producido un desfase entre el rápido aumento de la densidad de cálculo de los procesadores y el incremento más lento del ancho de banda de la memoria. Este problema de "muro de memoria" provoca que los procesadores esperen datos con frecuencia, lo que conduce a una infrautilización y plantea un reto sustancial para futuras mejoras del rendimiento.

NVIDIA y AMD han introducido las tecnologías NVLink e Infinity Fabric, respectivamente, para mejorar la interconectividad entre la CPU y la GPU, lo que resulta crucial para mejorar el ancho de banda entre los componentes lógicos.

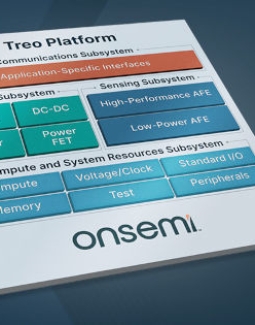

La incorporación a las arquitecturas de la nueva generación de memorias de alto ancho de banda (HBM), formadas por múltiples troqueles DRAM apilados verticalmente y conectados mediante vías de silicio (TSV), ofrece un aumento sustancial del ancho de banda entre la lógica y la memoria. Aunque antes se limitaban a las GPU, las HBM se están integrando ahora en las CPU, salvando la brecha de ancho de banda entre éstas y la DRAM tradicional. La Instinct MI300 de AMD ejemplifica esta tendencia al integrar HBM avanzadas con la CPU y la GPU en un único encapsulado. Las tecnologías de empaquetado de semiconductores 2,5D, como Chip on Wafer on Substrate (CoWoS) de TSMC, desempeñan un papel crucial en el aumento del número de puntos de E/S (entrada/salida), al tiempo que reducen la longitud de interconexión entre los componentes lógicos y de memoria, lo que mejora el rendimiento y reduce la latencia. Sin embargo, las nuevas cargas de trabajo de HPC, en particular las relacionadas con el entrenamiento de IA, exigen un ancho de banda de memoria aún mayor (más de 45x) debido a los frecuentes accesos a la memoria. El aumento de la velocidad de E/S puede mejorar el ancho de banda de HBM, pero está limitado por el mayor consumo de energía.

Para solucionar este problema, los nuevos diseños de procesadores se han centrado en aumentar la capacidad de la SRAM en el chip, ya que está situada cerca de los chips de procesamiento, lo que permite un mayor ancho de banda con interconexiones más densas y menor latencia. En las primeras implementaciones se utilizó la tecnología de encapsulado de unión híbrida 3D para unir un dado SRAM sobre un dado lógico en un paso de 9 μm, triplicando la capacidad SRAM. Para mejorar aún más el ancho de banda, el paso de la unión híbrida se redujo de 9 μm a 0,4 μm, lo que multiplicó por más de 300 la densidad del ancho de banda.

La óptica en coencapsulado es otro enfoque que está cobrando gran impulso en los últimos años. La comunicación óptica ofrece varias ventajas sobre la transmisión tradicional de señales eléctricas. Tiene menos pérdidas de transmisión, lo que reduce la degradación de la señal en las distancias. Además, la comunicación óptica es menos susceptible a la diafonía, que se produce cuando las señales interfieren entre sí, provocando errores en los datos. Además, las señales ópticas pueden alcanzar un mayor ancho de banda en comparación con sus homólogas eléctricas, lo que las hace ideales para aplicaciones de datos intensivos.

En resumen, para la próxima generación de sistemas de computación de IA, un gran ancho de banda entre lógica y lógica y entre lógica y memoria son tendencias de desarrollo cruciales. Las tecnologías avanzadas de empaquetado de semiconductores, como la unión híbrida 2,5D y 3D, junto con soluciones emergentes como la comunicación óptica, son fundamentales para permitir este crecimiento y superar los retos computacionales.

Autor: Dr. Yu-Han Chang, analista tecnológico senior de IDTechEx

Articulos Electrónica Relacionados

- Un sistema entrena a los drone... Si sigue las carreras de drones autónomos, es probable que recuerde las caídas tanto como las victorias. En las carreras de drones, los equipos compiten para ve...

- Los supercondensadores desafía... Un equipo que trabaja con Roland Fischer, Profesor de Química Inorgánica y Metal-Orgánica de la Universidad Técnica de Munich (TUM) ha desarrollado un supercond...

- Reducción y eliminación de los... La clave para una mayor adopción de los vehículos eléctricos (VE) serán modelos de menor coste y precio más asequible. El componente más caro de un VE es la bat...

- El comité COM-HPC de PICMG apr... congatec se complace en anunciar que el subcomité técnico PICMG COM-HPC ha aprobado el pinout (configuración) y el footprint (huella) de la nueva especificación...

- Digitalización en el sector ar... Usar máquinas de una manera económica y controlar su utilización es difícil para las pequeñas empresas artesanales. Los sistemas de software convencionales que ...

- Schneider Electric y Wärtsilä ... Schneider Electric y Wärtsilä han firmado un acuerdo de colaboración para crear una solución de energía sostenible ininterrumpida para alimentar las minas de li...

- Robot submarino para explorar ... El Centro de Automática y Robótica (CAR), un centro de investigación de la UPM y el CSIC, participa en el proyecto europeo UNEXMIN, cuyo objetivo es el desarrol...

- Los nuevos sensores de profund... Durante los últimos 10 años, el grupo Camera Culture en el Media Lab del MIT ha desarrollado innovadores sistemas de imágenes, desde una c&...

- Un chip de baja potencia y pro... En previsión de la era de la electrónica controlada por voz, los investigadores del MIT han construido un chip de baja potencia especializado para...

- Beneficios de coste y eficienc... La capacidad de proporcionar una mayor eficiencia energética y control de movimiento preciso están impulsando la adopción de los accionamientos eléctricos en in...

- La legislación española penali... ¿Cuáles son los principales escollos que un ciudadano español tiene que salvar si quiere implantar un sistema de autoconsumo energét...

- Tres nuevas tendencias en tecn... IDTechEx ha identificado tres nuevas megatendencias en el mundo de la tecnología:• Electrónica estructural (SE)• Electrónica impr...