Próxima generación de procesadores de IA de alta eficiencia energética RZ/V2H para robots autónomos

Este artículo presenta el MPU RZ/V2H, que permite tanto la IA de visión como las capacidades de control en tiempo real.

A medida que disminuya la población activa debido al descenso de la natalidad y al aumento de la población de edad avanzada, será necesario un procesamiento avanzado de inteligencia artificial (IA), como el reconocimiento del entorno, la decisión de acciones y el control del movimiento, en diversos aspectos de la sociedad, como fábricas, logística, atención médica, robots de servicio que operan en la ciudad y cámaras de seguridad. Los sistemas tendrán que manejar procesamientos avanzados de inteligencia artificial (IA) en tiempo real en diversos tipos de programas.

El RZ/V2H es capaz de responder a la evolución de la IA y a los sofisticados requisitos de estas aplicaciones. Este artículo presenta cómo el RZ/V2H resuelve los problemas de generación de calor, permite una alta velocidad de procesamiento en tiempo real y consigue un mayor rendimiento y un menor consumo de energía para los productos equipados con IA.

Resumen

A medida que disminuya la población activa debido al descenso de la natalidad y al aumento de la población de edad avanzada, será necesario un procesamiento avanzado de inteligencia artificial (IA), como el reconocimiento del entorno, la decisión de acciones y el control del movimiento, en diversos aspectos de la sociedad, como fábricas, logística, atención médica, robots de servicio que operan en la ciudad y cámaras de seguridad. Los sistemas tendrán que manejar el procesamiento avanzado de inteligencia artificial (IA) en tiempo real en varios tipos de programas. En particular, el sistema debe estar embebido en el dispositivo para permitir una respuesta rápida a su entorno en constante cambio. Sin embargo, los chips de IA. Al mismo tiempo, consumen menos energía mientras realizan el procesamiento avanzado de IA en dispositivos embebidos con limitaciones estrictas en cuanto a la generación de calor.

Para satisfacer estas necesidades del mercado, Renesas ha desarrollado el procesador reconfigurable dinámicamente DRP-AI3 (Dynamically Reconfigurable Processor for AI3) como acelerador de IA para el procesamiento de inferencia de IA de alta velocidad que combina el bajo consumo y la flexibilidad que requieren los dispositivos de vanguardia. Esta tecnología de procesador acelerador de IA reconfigurable, desarrollada durante muchos años, está embebida en la serie RZ/V de MPUs dirigidos a aplicaciones de IA.

RZ/V2H es un nuevo producto de gama alta de la serie RZ/V, que consigue una eficiencia energética aproximadamente 10 veces superior a la de los productos anteriores. El RZ/V2H es capaz de responder a la evolución de la IA y a los sofisticados requisitos de aplicaciones como los robots. Este artículo presenta cómo el RZ/V2H resuelve los problemas de generación de calor, permite una alta velocidad de procesamiento en tiempo real y consigue un mayor rendimiento y un menor consumo de energía para los productos equipados con IA.

Acelerador DRP-AI3 que procesa eficazmente modelos de IA depurados

Como tecnología típica para mejorar la eficiencia del procesamiento de la IA, la depuración está disponible para omitir cálculos que no afectan significativamente a la precisión del reconocimiento. Sin embargo, es habitual que los cálculos que no afectan a la precisión del reconocimiento existan aleatoriamente en los modelos de IA. Esto provoca una diferencia entre el paralelismo del procesamiento por hardware y la aleatoriedad de la depuración, lo que hace que el procesamiento sea ineficiente.

Para resolver este problema, Renesas optimizó su exclusivo acelerador de IA basado en DRP (DRP-AI) para la depuración. Analizando cómo las características de los patrones de depuración y un método de depuración están relacionados con la precisión del reconocimiento en los modelos típicos de IA de reconocimiento de imágenes (modelos CNN), identificamos la estructura de hardware de un acelerador de IA que puede lograr tanto una alta precisión de reconocimiento como una tasa de depuración eficiente, y la aplicamos al diseño del DRP-AI3. Además, se desarrolló un software para reducir el peso de los modelos de IA optimizados para este DRP-AI3. Este software convierte la configuración del modelo de depuración aleatoria en cálculo paralelo de alta eficiencia, lo que se traduce en un procesamiento de IA de mayor velocidad. En particular, la tecnología de soporte de depuración altamente flexible de Renesas (tecnología de depuración flexible N:M), que puede cambiar dinámicamente el número de ciclos en respuesta a los cambios en la tasa de depuración local en los modelos de IA, permite un control preciso de la tasa de depuración de acuerdo con el consumo de energía, la velocidad de funcionamiento y la precisión de reconocimiento requeridos por los usuarios.

Características de la arquitectura heterogénea en la que DRP-AI3, DRP y CPU operan de forma cooperativa

- Procesamiento multihilo y en cadena con el acelerador de IA (DRP-AI3), el DRP y las CPU.

- Aplicaciones robóticas de alta velocidad y baja fluctuación con DRP (hardware lógico cableado reconfigurable dinámicamente)

Los robots de servicio, por ejemplo, requieren un procesamiento avanzado de IA para reconocer el entorno circundante. Por otro lado, el procesamiento basado en algoritmos que no utiliza IA también es necesario para decidir y controlar el comportamiento del robot. Sin embargo, los procesadores integrados (CPU) actuales carecen de recursos suficientes para realizar estos distintos tipos de procesamiento en tiempo real. Renesas ha resuelto este problema desarrollando una tecnología de arquitectura heterogénea que permite que el procesador reconfigurable dinámicamente (DRP), el acelerador de IA (DRP-AI3) y la CPU trabajen juntos.

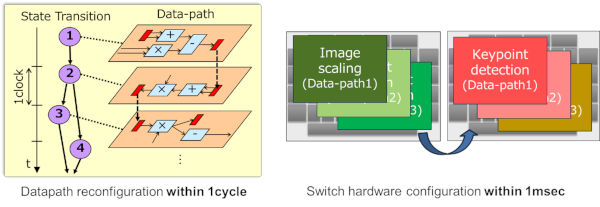

Como muestra la figura 1, el procesador reconfigurable dinámicamente (DRP) puede ejecutar aplicaciones mientras cambia dinámicamente la configuración de conexión de circuitos de las unidades aritméticas del chip en cada reloj de funcionamiento en función del contenido que se vaya a procesar. Como sólo se utilizan los circuitos aritméticos necesarios, el DRP consume menos energía que con el procesamiento de la CPU y puede alcanzar mayor velocidad. Además, en comparación con las CPU, donde los frecuentes accesos a la memoria externa debidos a pérdidas de caché y otras causas degradan el rendimiento, el DRP puede construir las rutas de datos necesarias en hardware con antelación, lo que se traduce en una menor degradación del rendimiento y una menor variación de la velocidad de funcionamiento (jitter) debida a los accesos a la memoria.

El DRP es especialmente eficaz en el procesamiento de datos en flujo, como el reconocimiento de imágenes, donde la paralelización y el pipelining mejoran directamente el rendimiento. Por otro lado, programas como los de decisión y control del comportamiento de robots requieren procesamiento mientras cambian las condiciones y procesamiento de detalles en respuesta a cambios en el entorno circundante. El procesamiento por software de la CPU puede ser más adecuado para esto que el procesamiento por hardware, como en el DRP. Es importante distribuir el procesamiento en los lugares adecuados y operar de forma coordinada. La tecnología de arquitectura heterogénea de Renesas permite que el DRP y la CPU trabajen juntos.

Figura 1: Características del procesador flexible reconfigurable dinámicamente (DRP)

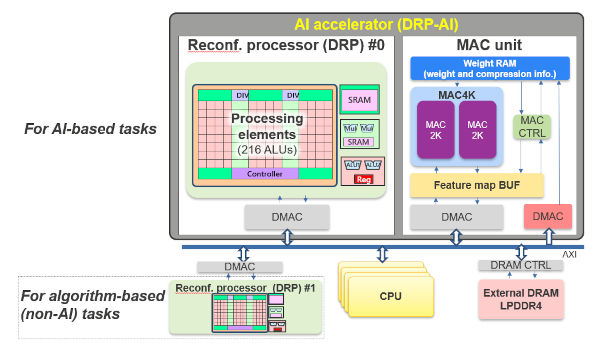

En la figura 2 se muestra una visión general de la arquitectura del MPU y el acelerador de IA (DRP-AI3). Las aplicaciones robóticas utilizan una sofisticada combinación de algoritmos de reconocimiento de imágenes basados en IA y algoritmos de decisión y control no basados en IA. Por tanto, una configuración con un DRP para el procesamiento de IA (DRP-AI3) y un DRP para algoritmos no basados en IA aumentará significativamente el rendimiento de la aplicación robótica.

Figura 2: Configuración de arquitectura heterogénea basada en DRP-AI 3

Resultados de la evaluación

(1) Evaluación del rendimiento de procesamiento del modelo de IA

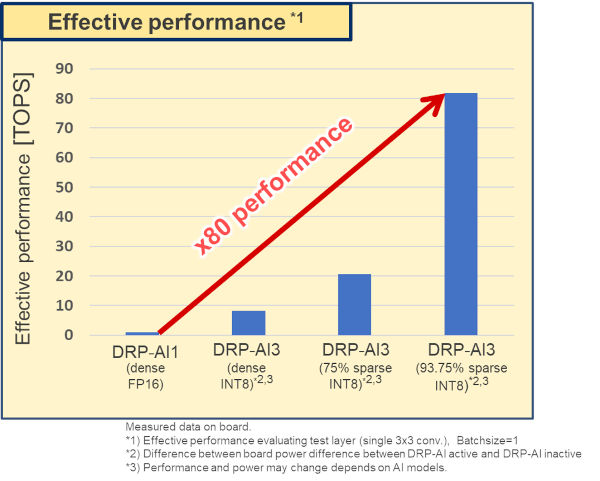

El RZ/V2H equipado con esta tecnología ha alcanzado un máximo de 8 TOPS (8 billones de operaciones de suma de productos por segundo) para el rendimiento de procesamiento del acelerador de IA.Además, para los modelos de IA que han sido depurados, el número de ciclos de operación puede reducirse en proporción a la cantidad de depuración, con lo que se consigue un rendimiento de procesamiento de modelos de IA equivalente a un máximo de 80 TOPS en comparación con los modelos antes de la depuración. Esto es unas 80 veces superior al rendimiento de procesamiento de los productos RZ/V anteriores, una mejora significativa del rendimiento que puede seguir suficientemente el ritmo de la rápida evolución de la IA (Figura 3).

Figura 3: Comparación del rendimiento máximo medido de DRP-AI3

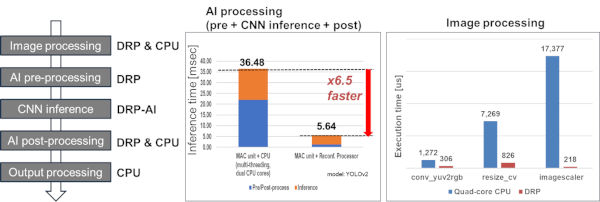

Por un lado, a medida que se acelera el procesamiento de la IA, el tiempo de procesamiento de imágenes basado en algoritmos sin IA, como el procesamiento previo y posterior a la IA, se está convirtiendo en un relativo cuello de botella. En las AI-MPU, una parte del programa de procesamiento de imágenes se descarga en el DRP, lo que contribuye a mejorar el tiempo total de procesamiento del sistema.(Figura 4)

Figura 4: La arquitectura heterogénea acelera el procesamiento del reconocimiento de imágenes (medido por el chip de prueba)

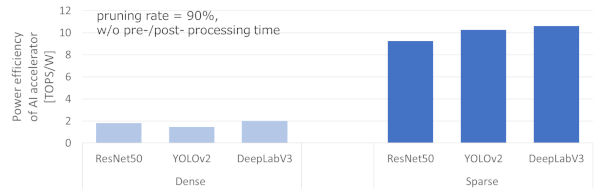

En términos de eficiencia energética, la evaluación del rendimiento del acelerador de IA demostró el máximo nivel mundial de eficiencia energética (aproximadamente 10 TOPS por vatio) al ejecutar los principales modelos de IA. (Figura 5)

Figura 5: Eficiencia energética de modelos reales de IA (medida por chip de prueba)

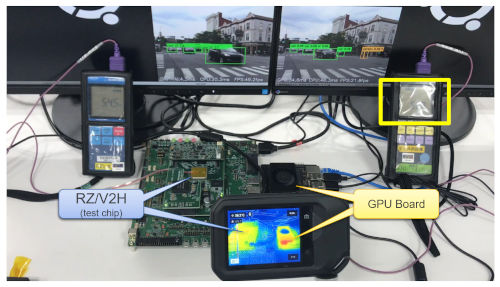

También demostramos que el mismo procesamiento de IA en tiempo real podía realizarse en una placa de evaluación equipada con el RZ/V2H, sin ventilación forzada, a temperaturas comparables a las de los productos de la competencia equipados con ventiladores.(Figura 6)

Figura 6: Comparación de la generación de calor entre una placa RZ/V2H sin ventilación forzada y una GPU con ventilador

(2) Ejemplos de aplicaciones con robots

Por ejemplo, la localización y mapeo simultáneo SLAM (Simultaneous Localization And Mapping), una de las aplicaciones típicas de los robots, tiene una configuración compleja que requiere múltiples procesos de programa para el reconocimiento de la posición del robot en paralelo con el reconocimiento del entorno mediante procesamiento de IA.El DRP de Renesas permite al robot cambiar de programa instantáneamente, y el funcionamiento en paralelo con un acelerador de IA y la CPU ha demostrado ser unas 17 veces más rápido que el funcionamiento de la CPU sola, y reducir el consumo de energía a 1/12 del nivel del funcionamiento de la CPU sola.

Conclusión

Renesas ha desarrollado RZ/V2H, un procesador de IA único que combina el bajo consumo y la flexibilidad que requieren los puntos finales, con capacidades de procesamiento para depurar modelos de IA, y 10 veces más eficiente en consumo (10 TOPS/W) que los productos anteriores.

Renesas lanzará oportunamente productos que respondan a la evolución de la IA, que se espera sea cada vez más sofisticada, y contribuirá a desplegar sistemas que respondan a los productos de punto final de forma inteligente y en tiempo real.

Autor: Shingo Kojima, Ingeniero Principal de Procesamiento Integrado, Renesas Electronics

Información relacionada

- RZ/V2H: https://www.renesas.com/rzv2h

- DRP-AI: acelerador de IA patentado por Renesas que combina un alto rendimiento de inferencia de IA con un bajo consumo de energía

Articulos Electrónica Relacionados

- Controladores USB Power Delive... Microchip anuncia desde Computex Taipei la nueva familia de controladores USB Power Delivery (UPD) UPD100X con protocolo estándar de alimentación y carga ...

- MCU de 32 Bit Bolster para alt... Renesas Electronics Europe presenta un microcontrolador de ayuda al desarrollo de aplicaciones basadas en el contacto en el hogar, la construcción, autom...

- Microcontroladores Renesas RX2... Renesas Electronics Corporation ha anunciado la expansión de sus grupos RX24T y RX24U de microcontroladores de 32 bits (MCU) para incluir nuevos modelos toleran...

- Microcontroladores Cortex-M4 d... Mouser Electronics, Inc distribuye los microcontroladores LPC546xx de 32 bits de NXP Semiconductors. Estos dispositivos mejoran el consumo dinámico de en...

- MCU MOTIX™ TLE989x de Infineon... Mouser ya tiene en stock los microcontroladores (MCU) MOTIX™ TLE989x de Infineon Technologies. Ampliando la ya amplia y acreditada cartera de CI de potencia int...

- Microprocesadores Renesas MPU ... Renesas Electronics Corporation ha anunciado la ampliación de su serie RZ/V de microprocesadores (MPU) con los nuevos MPU RZ/V2L, diseñados para aplicaciones bá...

- Módulo de microcontrolador de ... Ante la expansión de IoT (Internet de las Cosas) más allá de la automatización del hogar, su mayor presencia en el control del hogar – como por ejemplo de siste...

- MPU de alta precisión RZ/V2L d... Mouser ya tiene en stock los microprocesadores de IA RZ/V2L de Renesas Electronics. El RZ/V2L es ideal para los ingenieros que buscan una solución de inteligenc...

- Renesas completa el lanzamient... Renesas Electronics amplía su cartera de microcontroladores (MCU) dentro de la plataforma Renesas Synergy ™ para cubrir una gama aún m&aacut...

- Microchip MCU PIC32CM Lx con s... Mouser ofrece ya los microcontroladores de muy bajo consumo PIC32CM LE00, LS00 y LS600 (PIC32CM Lx) de Microchip Technology. Cada uno de los microcontroladores ...

- Microcontrolador RL78 / I1D de... Renesas Electronics anuncia la disponibilidad del grupo de microcontroladores RL78/I1D. El grupo del RL78/I1D hace realidad el consumo de energía más bajo...

- Microcontroladores Renesas RA0... Renesas Electronics Corporation ha presentado la serie de microcontroladores (MCU) RA0 basados en el procesador Arm® Cortex®-M23. Los RA0 consumen sólo 84,3μA/M...