Menor consumo en modo reposo de 13,7 nW / Mbit y 1,84 ns de lectura de alta velocidad con la nueva SRAM embebida

Renesas Electronics ha anunciado el desarrollo exitoso de una nueva tecnología de circuitos SRAM de baja potencia que puede ser incorporada en productos estándar específicos de aplicación (ASSPs) para IoT (Internet of Things), electrónica doméstica y aplicaciones de atención médica. La nueva tecnología proporciona una función de conmutación dinámica, con una sobrecarga de baja potencia, entre la operación activa, en la que el núcleo de la CPU realiza operaciones de lectura y escritura de la SRAM incorporada y el modo de espera, en el que se conservan los datos almacenados.

Renesas Electronics ha anunciado el desarrollo exitoso de una nueva tecnología de circuitos SRAM de baja potencia que puede ser incorporada en productos estándar específicos de aplicación (ASSPs) para IoT (Internet of Things), electrónica doméstica y aplicaciones de atención médica. La nueva tecnología proporciona una función de conmutación dinámica, con una sobrecarga de baja potencia, entre la operación activa, en la que el núcleo de la CPU realiza operaciones de lectura y escritura de la SRAM incorporada y el modo de espera, en el que se conservan los datos almacenados.

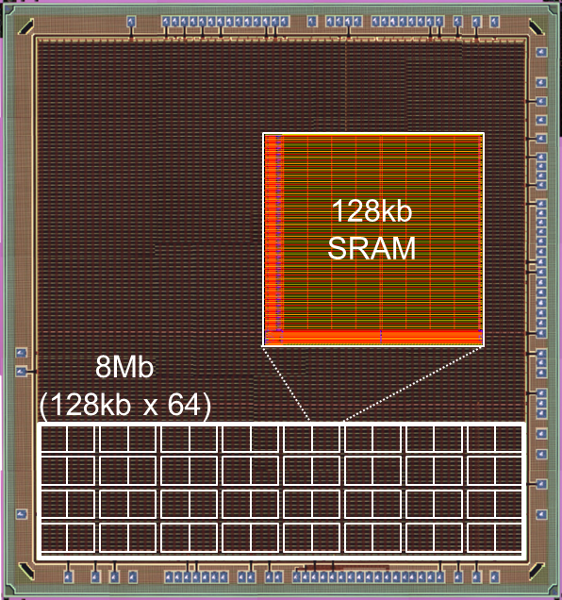

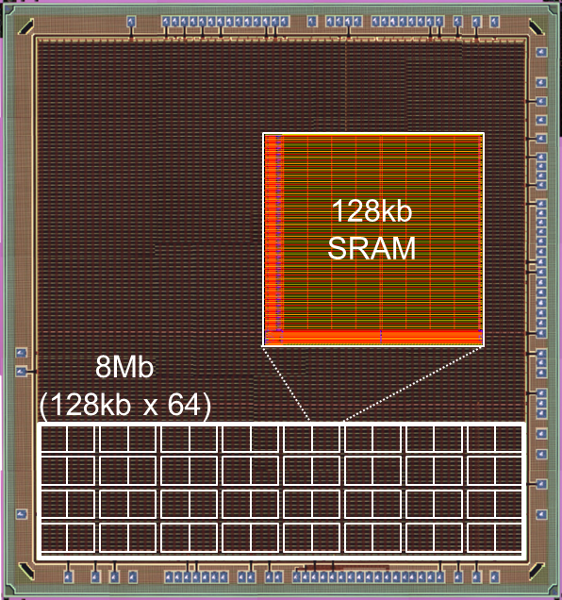

Renesas aplicó su propio procesador de silicio de nodos de 65 nanómetros (nm) en el delgado BOX (SOTB, Nota 1) para el desarrollo de prototipos de SRAM embebida. El prototipo SRAM logra al mismo tiempo, tanto el tiempo de lectura de alta velocidad de 1,8 ns durante el funcionamiento activo, como el consumo de energía ultrabajo de 13,7 nW / Mbit en modo reposo. La SRAM alcanza las características de consumo de energía en modo de espera más bajas (Nota 2) de la industria, que es sólo una milésima del consumo de energía durante el modo de espera, utilizando el control dinámico de polarización posterior del sustrato, aprovechando la estructura SOTB.

Recientemente, en el mercado de IoT en rápido crecimiento, todas las aplicaciones estarán conectadas de forma inalámbrica y, por lo tanto, hay fuertes deseos de funcionamiento libre de batería, que utiliza fuentes de energía naturales como luz, vibración o calor y menor consumo de energía para una mayor duración de la batería. Además, cuando se logra una vida útil de la batería más larga, ya no será necesario reemplazar la batería, lo que permite que las aplicaciones no requieran mantenimiento.

Al mismo tiempo, lograr la miniaturización de productos finales es esencial para el desarrollo de aplicaciones de IoT. La reducción del consumo de energía del ASSP al menos un orden de magnitud permitiría la miniaturización, ya que reduce la capacidad de la batería actualmente utilizada. Como un esfuerzo para reducir el consumo de energía en ASSPs para el IoT, existe una técnica en la que la aplicación es operada de forma intermitente, estando normalmente en el modo de espera y sólo pasando al modo activo cuando se requiere procesamiento de datos. En particular, el procedimiento más utilizado para reducir el consumo de energía en modo de espera es cortar la alimentación al circuito después de guardar los datos necesarios, ya sea en un dispositivo externo o en una memoria interna no volátil. Aunque este método es eficaz cuando los tiempos de espera son relativamente largos, en sistemas que frecuentemente alternan entre el modo activo y el modo en espera, el ahorro de datos en la memoria no volátil y la operación de reinicio se convierte en una sobrecarga significativa. Incluso hay casos en los que, inversamente, esto realmente aumenta el consumo de energía.

La nueva tecnología adopta un método en el que se reduce el consumo de energía de la SRAM incorporada en modo de espera. Esto permite que la operación intermitente se realice con frecuencia sin llevar a un mayor consumo de energía, por lo que no es necesario guardar datos en la memoria no volátil, lo que conduce a una eficiencia de potencia mejorada.

Los esfuerzos anteriores de Renesas relacionados con la SRAM embebida incluyen un prototipo de SRAM embebida con una estructura HKMG (high-k metal gate) de 28 nm y una SRAM embebida de alto rendimiento con una estructura de transistor FinFET (Fin field-effect transistor) de 16 nm, las cuales adoptan tecnologías de proceso de vanguardia. Estas tecnologías embebidas de SRAM han sido adoptadas en el sistema de información y entretenimiento para automoción de Renesas R-Car (SoCs). Renesas desarrolló una tecnología de circuitos que controla dinámicamente el sesgo (bias) del sustrato mediante la tecnología de proceso SOTB y permite que la corriente de fuga en modo de reposo se reduzca a aproximadamente a una milésima parte de la potencia en comparación con el modo de espera normal.

Características clave de la nueva tecnología SRAM incorporada:

1) Alcanza la potencia de modo de espera más baja de la industria de 13,7 nW / Mbit, así como una operación de lectura de alta velocidad de 1,84 ns mediante el uso de control de polarización de sustrato que aprovecha la estructura SOTB

Recientemente, la miniaturización de los procesos de semiconductores y el reto de la escala de voltaje están causando problemas; Tales como el aumento de la corriente de fuga debido al valor de umbral bajo de los elementos del dispositivo semiconductor y el deterioro del voltaje de límite inferior operativo debido a las variaciones crecientes en los elementos del dispositivo.Estos problemas producen un mayor consumo de energía en el modo de espera y una mayor potencia operativa debido a la incapacidad para reducir los voltajes de funcionamiento, lo que hace que disminuir el consumo de energía sea difícil.

Para responder a este problema, Renesas adoptó la tecnología de proceso SOTB desarrollada internamente, que suprime eficientemente las variaciones entre los elementos del dispositivo y mejora la relación de corriente de encendido / apagado, y ha prototipado una SRAM incorporada usando la nueva tecnología. La tecnología de proceso SOTB difiere de la estructura de transistores planar formada en el sustrato de silicio en tecnologías de procesos anteriores, ya que una película de óxido (óxido enterrado) está enterrada bajo una delgada capa de silicio sobre el sustrato de la oblea. La tecnología permite transistores de canal sin dopante que no requieren dopado de la capa de silicio de película delgada. Al hacer que la estructura sea una estructura de canal sin contaminante, las variaciones en las características de umbral del transistor pueden reducirse a aproximadamente un tercio de las del transistor de estructura global de tipo plano anterior. Esta reducción en las variaciones tiene un efecto similar al de la estructura FinFET adoptada en los SoC de última generación. La reducción de las variaciones en el rendimiento del transistor logra un funcionamiento estable a bajas tensiones alrededor de 0,5 V. Además, la adopción de una capa delgada BOX en la tecnología de proceso SOTB permite cambios significativos en las características de valor umbral de los transistores controlando el potencial del sustrato de silicio bajo el BOX. Esta es una característica que no pudo lograrse con la estructura a granel planar anterior o la estructura FinFET. Aprovechando esta característica, Renesas proporciona un regulador integrado que puede controlar dinámicamente el sesgo de substrato SRAM incorporado que permite seleccionar uno de los tres modos de funcionamiento (modo normal, modo de baja potencia y modo de alta velocidad) o modo de espera De acuerdo con el estado del sesgo de sustrato aplicado.

Utilizando este regulador, Renesas confirmó que cuando se requiere un procesamiento computacional de alta carga, cambiando del modo normal al modo de alta velocidad, es decir, al establecer el potencial del sustrato de polarización cero a un sesgo directo, el tiempo de acceso de lectura cambia de 4,58 Ns a 1,84 ns, logrando así un aumento de la velocidad de 2,5 veces más rápido en comparación con el modo normal. Por el contrario, en el modo de espera, aplicando una polarización inversa como potencial del sustrato, la corriente de fuga se reduce en tres órdenes de magnitud a 13,7 nW / Mbit, que es sólo una milésima del consumo de energía durante el modo de espera Potencia de fuga en modo normal.

2) Cuando la polarización del substrato y la señal en respuesta a la carga computacional se controlan dinámicamente, se puede lograr tanto un funcionamiento de alta velocidad como un bajo consumo de energía según el modo de funcionamiento. Es necesario garantizar un funcionamiento estable en todas las condiciones de polarización. Incluso si las variaciones en las características de la SRAM embebidda se reducen al adoptar la estructura SOTB en comparación con las de los dispositivos de estructura global de tipo planar anteriores, dichas variaciones no pueden reducirse a cero. Por lo tanto, se hace importante asegurar márgenes de diseño de tal manera que la celda de memoria con la variación más grande pueda funcionar. En ASSPs para aplicaciones IoT, hay muchos casos en los que se colocan varias macros SRAM alrededor del chip. El margen de diseño requerido en cada unidad de macro SRAM individual variará de acuerdo con la probabilidad con la que se incluye en la macro la celda de memoria con las variaciones más grandes. Normalmente, se asignaron los mismos márgenes de diseño de peor condición a cada macro, de manera que el funcionamiento en las peores condiciones podría garantizarse de manera fiable para todas las macros del chip. Sin embargo, eso significaba que siempre había macros para las cuales los márgenes eran excesivos.

Para mejorar esta situación, Renesas propuso un método de circuito de réplica en el que el ancho de pulso de lectura podría optimizarse en forma de grano fino (Nota 3) para eliminar los márgenes de diseño excesivos. Esto hace posible reducir la potencia activa hasta en un 20% durante las operaciones de lectura.

La SRAM embebida de baja potencia logra tanto un bajo consumo de energía en modo reposo bajo, yvelocidad de funcionamiento aumentada, que eran difíciles de conseguir con el progreso continuo de la miniaturización del proceso semiconductor. Al permitir que las ASSP adopten la SRAM embebida con la estructura SOTB, Renesas planea apoyar tanto la operación de recolección de energía como contribuir al desarrollo de aplicaciones IoT sin mantenimiento, que no requieren reemplazo de baterías. Además, al incluir la SRAM embebida en ASSPs de baja potencia que se fabrican utilizando el proceso SOTB de 65 nm, Renesas planea contribuir aún más a la creación de una sociedad más inteligente.

Más información o presupuesto

Nota 1: BOX: óxido enterrado

Nota 2: A partir del 8 de junio de 2017, según investigación de Renesas

Nota 3: En pequeñas unidades macro

Articulos Electrónica Relacionados

- Memorias DDR4 que optimizan el... Crucial lanza sus nuevas memorias DDR4 Ballistix Sport y Ballistix Tactical especialmente concebidas para optimizar el rendimiento de los videojuegos. Estos nue...

- Transistores digitales RET de ... Nexperia ha anunciado la primera familia de transistores de 80 V equipados con resistencia. Estos nuevos RET o "transistores digitales" proporcionan suficiente ...

- Samsung produce de manera masi... Samsung Electronics Co., Ltd. ha anunciado la producción en masa de las memorias DDR3 más avanzadas, basadas en una nueva tecnología de procesos de 20 nanómetro...

- Procesadores de 16 nm para rou... Broadcom Limited ha anunciado su última serie de procesadores basados en conocimiento heterogéneos (KBPs), el BCM15000 (BCM15K), diseñada p...

- JEDEC 5.1 presenta la memoria ... La última versión JEDEC 5.1 define una serie de características nuevas y mejoradas que serán útiles a los diseñadores ...

- IGBT de 600 V de IR optimizado... International Rectifier lanza al mercado una familia de IGBT de 600 V homologados para el automóvil y optimizados para aplicaciones de control de motores de vel...

- Solución de memoria para almac... Toshiba Memory Europe GmbH (TME) ha anunciado el lanzamiento de una nueva solución de memoria para almacenamiento (SCM): XL-FLASH ™. Basado en la innovadora tec...

- Memoria NAND Flash interfaz de... Toshiba Electronics Europe ha lanzado una nueva línea de productos memoria SLC NAND Flash de 24nm para aplicaciones embebidas compatibles con la interfaz...

- Farnell tiene en stock los reg... Farnell ya tiene en stock los reguladores de tensión PoL Gen 2.1 SupIRBuck™ de International Rectifier. La nueva familia de productos altamente efic...

- MOSFET de Súper Unión con cuat... Toshiba Electronics Europe GmbH (“Toshiba”) ha añadido otros cuatro dispositivos MOSFET de potencia de 650 V superjunction (super unión) de canal N para ampliar...

- Large PIN Fotodiodos de VISHAY RC Microelectrónica presenta el catálogo mejorado de sensores de luz (Infrarrojos y luz visible) de su representada VISHAY INTERTECHNOLOGY. Dise&n...

- MOSFET de potencia PQFN2x2 ult... International Rectifier amplía su oferta de encapsulados con la introducción de un encapsulado PQFN de 2 mm x 2 mm que incorpora la tecnología más avanzada de s...